The greater the frequency of the FSB bus. Sufficient tire speed of the motherboard. System tire - what is it

The central computer processor has a number technical characteristicsthat determine the most important characteristic of any processor - its productivity And the meaning of each of them is helpful to know. Why? In order to further navigate to navigate in reviews and testing, as well as labels of the CPU. In this article, I will try to reveal maintenance specifications Processor In understandable presentation.

The main technical characteristics of the central processor:

- Clock frequency;

- Discharge;

- Cache memory;

- Number of Cores;

- The frequency and the discharge of the system tire;

Consider details these features

Clock frequency

Clock frequency -executive speed of the commands with the central processor.

Tact - time interval required to perform an elementary operation.

In the near past clock frequency The central processor was identified directly with its productivity, that is, the higher the clock frequency of the CPU, the more productory. In practice, we have a situation where Processors with different frequency have the same performance, because in one clock can perform a different number of commands (depending on the kernel design, bus bandwidth, cache memory).

The processor clock frequency is proportional to the system tire frequency ( see below).

Bigness

The prohibition of the processor is the value that determines the amount of information that the central processor is able to process for one tact.

For example, if the processor's discharge is 16, it means that it is able to process 16 bits of information for one tact.

I think everyone understands that the higher the processor's discharge, the large amounts of information it can process.

Usually, the greater the processor's discharge, the performance is higher.

Currently, 32- and 64-bit processors are used. The prohibition of the processor does not mean that it is obliged to perform commands with the same bit.

Cache memory

First of all, answer the question of what cache memory is?

Cash memory is the high-speed computer memory, intended for temporary storage of information (code of executable and data) required by the central processor.

What data are stored in cache?

The most commonly used.

What is the purpose of cache memory?

The fact is that the performance of RAM is relatively with the capacity of the CPU much lower. It turns out that the processor is waiting for data from RAM - which reduces the performance of the processor, and therefore the performance of the entire system. Cache memory reduces processor waiting time, retaining data and code of executable programs to which the processor has most frequently addressed (the difference of the Cash memory from the computer's RAM is the speed of the cache-memory of tens of times higher).

Cash memory, as well as normal memory, has a bit. The higher the bitmap of the cache memory with large amounts of data can it work.

Three level cache memory differences: cache memory first (L1), second (L2) and third (L3). Most often in modern computers apply the first two levels.

Consider in more detail all three levels of cache.

Cache memory first Level is the fastest and most expensive memory.

The first-level cache memory is located on the same crystal with the processor and works at the CPU frequency (hence the greatest speed) and used directly to the core of the processor.

The container of the first level cache is small (by virtue of high costs) and calculated kilobytes (usually no more than 128 KB).

Second Level Cache - This is a high-speed memory that performs the functions as the L1 cache. The difference between L1 and L2 is that the latter has a lower speed, but a larger volume (from 128 Kbytes to 12 MB), which is very useful for the performance of resource-intensive tasks.

Third-level cache Located on the motherboard. L3 is significantly slower than L1I L2, but faster RAM. It is clear that the volume L3 is larger than L1I L2. The third-level cache memory is found in very powerful computers.

Number of Cores

Modern processor manufacturing technologies allow for more than one kernel in one case. The presence of several cores significantly increases the performance of the processor, but this does not mean that the presence n. nuclei gives an increase in productivity in n. time. In addition, the problem of processor multi-core lies in the fact thatand today, there are relatively few programs written, taking into account the presence of several cores in the processor.

The main characteristics of the tire are its discharge and frequency of work. The frequency of the tire is the clock frequency with which data is exchanged between the processor and the computer bush.

Naturally, the higher the size and frequency of the system tire, the higher the processor performance.

High tire data transfer rate provides the ability to quickly receive a processor and computer devices. necessary information and teams.

The frequency of operation of all modern processors is several times higher than the frequency of the system bus, so the processor works on as much as it allows it to be a system tire. The value for which the processor frequency exceeds the system tire frequency is called a multiplier.

Today, together with IT expert experts, we understand that such a unlocked multiplier (multiplication ratio) is, and for which it is needed.

Quite often we are confronted in the news so that Intel or AMD has released such a process with an unlocked multiplier to the joy of enthusiasts and overclockers. It is clear that the multiplier is only in processors, and that it can be blocked and unlocked (allowed to change) by the processor manufacturer.

The processor overclocling with a unlocked multiplier, RAM and motherboard is a way to customize the computer. You can customize power, voltage, kernel, memory, memory parameters, and other important system indicators to maximize performance increases. Overclocking accelerates components and gameplay. It also allows you to optimize tasks that require a large number of processor resources, such as image processing and transcoding.

"Unlocked multiplier" means that in BIOS personal computer You can change the processor multiplier down or up. So what is this multiplier? Before answering this question, let's find out how the frequency of the processor is obtained.

Take motherboard from specified frequency Tires (FSB), for example 533 MHz (Meghertz), and a processor with a multiplier 4.5. As a result (533 x 4.5), we obtain the desired clock frequency of the processor in 2398.5 MHz. Now, if you raise the multiplier to 7.5, then at the exit we will get the speed gain of 1599 megahertz. If we reduce to 3.5 - the frequency of the processor drops to 1.8 GHz.

The formula of the face of the multiplier has a similar look:

- FSB (System Board Tire Frequency - Motherboard)

- CPU Multiplier (CPU Multiplier)

- DDR Multiplier (it is 400/533/667/800 AKA 1 / 1.33 / 1.66 / 2.0)

for example, DDR2 \u003d FSB * MULTUPLIER * 2 (clarified)

Ordinary processors go on sale with a multiplier blocked for an increase. The manufacturer can be understood. After all, it turns out that why should we buy a processor for the conditional 200 dollars when you can buy a model easier for $ 100, change one parameter in the BIOS and get the same processor for $ 200? Lower the multiplier can be from any processor.

However, the blocked multiplier does not mean that overclocking the processor, that is, it is impossible to increase its frequency. After all, the processor takes the basis of the motherboard. Therefore, the enthusiast simply increases the motherboard's frequency (system bus) and receives a higher frequency of the processor without increasing the multiplier.

Processors Extreme Edition Intel and Black Edition - AMD comes on sale with unlocked multipliers. Also, the Intel processor with a unlocked multiplier can be identified by the letter K in the title. For example, 3570 and 3570k. The second is unlocked.

These processors are noticeably more expensive than their blocked fellows and are focused on computer enthusiasts and overclockers - people engaged in overclocking computer iron for the result that can be fixed and demonstrated to the community. An ordinary person unlocked multiplier can give a reserve of strength to upgrade the system for a couple of years. When it seems that the computer stopped "pull", you can simply disperse its frequency

Components inside PC interact with each other in various ways. Most internal components, including processor, cache, memory, expansion cards and storage devices interact with each other with one or more tire (BUSES).

The bus in computers is a channel by which information is transmitted between two or several devices (usually a tire connecting only two devices is called porto. - Port). The bus usually has access points, or a place to which the device can connect to convert itself into part of the bus, and the device on the bus can send information to other devices and receive information from other devices. The concept of the tire is rather common both for the "insides" of the PC and for the outside world. For example, a telephone connection in the house can be read by a bus: the information is transmitted over the wiring in the house and you can connect to the "bus" by setting the phone socket by connecting the phone to it and lifting the phone tube. All telephones on the bus can share (Share) information, i.e. speech.

This material is devoted to the tires of modern RS. Initially, tires and their characteristics are discussed, and then the most common PC in the world is discussed in detail. i / O Tires (INPUT / OUTPUT BUS), also called tires expansion (Expansion Buses).

Tire features and characteristics

RS tires are the main "paths" data on the motherboard. The main one is system tire (System Bus), which connects the processor and the main RAM memory. Previously, this tire was called local, and in modern RS called front tire (FRONT SIDE BUS - FSB). The characteristics of the system tire are determined by the processor; The modern system tire has a 64 bits width and operates at a frequency of 66, 100 or 133 MHz. Signals of such a high frequency create electrical interference and put other problems. Therefore, the frequency must be reduced so that the data reaches expansion cards (Expansion Card), or Adapters (Adapters), and other more remote components.

However, the first RS had only one bus that was common to the processor, RAM memory and I / O components. The first and second generation processors operated with a low synchronization frequency and all system components could maintain such a frequency. In particular, such an architecture made it possible to expand the RAM capacitance using expansion cards.

In 1987, Compaq developers decided to separate the system tire from the I / O bus so that they could work at different speeds. Since then, such a multishing architecture has become an industrial standard. Moreover, modern PCs have several input-output tires.

Shin hierarchy

The RS has a hierarchical organization of various tires. Most modern RS has, at least four tires. The tire hierarchy is explained by the fact that each tire is increasingly moving away from the processor; Each tire is connected to the above level, combining various components of the PC. Each tire is usually slower than the tire above it (for an obvious reason - the processor is the fastest device in the RS):

- Tire of the inner cache: This is the fastest tire that connects the processor and internal L1 cache.

- System bus: This is a second-level system bus that connects the memory subsystem with a chipset and processor. In some systems, the processor and memory tires are the same. This tire until 1998 worked at a speed (synchronization frequency) of 66 MHz, and then it was increased to 100 MHz and even 133 MHz. In Pentium II processors, architecture with double independent bus (Dual Independent Bus - DIB) - the only system tire is replaced with two independent bus. One of them is designed to access the main memory and is called front tire (Frontside Bus), and the second - to access L2 cache and is called rear tire (Backside Bus). The presence of two tires increases the PC performance, since the processor can simultaneously receive data from both tires. In motherboards and fifth generation chipsets, L2-cache is connected to a standard memory bus. Note that the system tire is also called Main tire (Main Bus) tire processor (Processor Bus) memory bus (Memory Bus) and even local tire (Local Bus).

- Local I / O Tire: This high-speed I / O bus is used to connect rapid peripheral memory to memory, chipset and processor. Type of tire use video cards, disk drives and network interfaces. The most common local I / O tires are VESA Local Bus (VLB) and Peripheral Component InterConnect bus (PCI).

- Standard I / O bus: The "deserved" standard I / O bus is connected to the three tires, which is used for slow peripheral devices (mouse, modem, sound cards, etc.), as well as for compatibility with old devices. In almost all modern PCs such a bus is the ISA bus (Industry Standard Architecture - standard industrial architecture).

- Universal sequential tire (Universal Serial Bus - USB), which allows you to connect up to 127 slow peripheral devices using Haba (HUB) or loop connections (daisy-chaning) devices.

- Speed \u200b\u200bSerial Tire IEEE 1394 (FireWire)intended for connecting to PC digital cameras, printers, TVs and other devices that require exceptionally high bandwidth.

Multiple I / O tire connecting various peripherals with the processor, connect to the system bus using bridge (Bridge) implemented in the chipset. The system chipset manages all tires and ensures that each device in the system correctly interacts with each other device.

In the new RS there is an additional "tire", which is specifically designed only for graphic interaction. In fact, this is not a tire, but port - Accelerated Graphics Port (Accelerated Graphics Port - AGP). The difference between the bus and the port is that the bus is usually calculated on the separation of the media by several devices, and the port is intended only for two devices.

As shown earlier, the I / O tires are actually an extension of the system tire. On the motherboard, the system tire ends with a chipset chipset that forms a bridge to an I / O bus. Tires play a crucial role in the exchange of data in the PC. In fact, all PC components, with the exception of the processor, interact with each other and the RAM system memory through various I / O bus, as shown in the figure on the left.

Address and Data Tires

Each tire consists of two different parts: data bus (Data Bus) and Tire address (ADDRESS BUS). Speaking of the tire, most people understand the data bus; On the lines of this tire are transmitted by the data. The address bus is a set of lines whose signals are determined where to transmit or where to receive data.

Of course, there are signal lines for controlling the operation of the bus and signaling of data availability. Sometimes these lines are called bus tire (Control Bus), although often they are not mentioned.

Bus width

The tire is a channel for which "flows" information. The wider bus, the more information can "flow" through the channel. The first ISA bus in IBM PC had 8 bits width; The universal ISA bus used now has a width 16. Other I / O bus, including VLB and PCI, have a 32 bits width. The width of the system tire in the PC with Pentium processors is 64 bits.

The width of the address bus can be determined regardless of the width of the data bus. The width of the address bus shows how many memory cells can be addressed when data transmission. In modern PC, the width of the address bus is 36 bits, which ensures the addressing of the memory capacity of 64 GB.

Speed \u200b\u200b(speed) tires

Tire speed (Bus Speed) Shows how many bits of information can be transmitted for each tire conductor per second. Most of the tires are transmitted one-bit on the synchronization clock, although new tires, such as AGP, can transmit two data bits in synchronization cycle, which doubles performance. In the old ISA bus to transmit one bit, two synchronization cycle requires, which reduces the performance twice.

Bus bandwidth

|

Bandwidth bandwidth (Bandwidth) is also called throughput (Throughput) and shows a total amount of data that can be transmitted over the bus for this unit of time. The table shows theoretical Passing capacity of modern I / O tires. In fact, the tires do not reach theoretical indicator due to service losses for the execution of teams and other factors. Most tires can operate at different speeds; The following table shows the most typical values.

We will make a remark about the last four lines. Theoretically, the PCI bus can be expanded to 64 bits and a speed of 66 MHz. However, for the reasons for compatibility, almost all PCI tires and device devices are calculated only at 33 MHz and 32 bits. AGP relies on theoretical standard and runs 66 MHz, but retains 32 bits width. AGP has additional modes X2 and X4, which allow the port to perform data transfer two or four times in synchronization tact, which increases the efficient tire speed to 133 or 266 MHz.

Tire Interface

In a multi-tire system, the chipset should provide schemes for combining tires and interacting the device on one bus with a device on another bus. Such schemes are called bridge (Bridge) (Note that the bridge is also called a network device for connecting two differentty networks). The most common PCI-ISA bridge, which is a component of a system chipset for PC with Pentium processors. The PCI bus also has a bridge to the system bus.

Mastering tires

In tires with a large bandwidth, every second of the channel passes a huge amount of information. Usually, the processor is required to manage these gears. In fact, the processor acts as a "mediator" and, as often happens in the real world, it is much more efficient to remove the intermediary and directly perform transmissions. For this, devices that can control the bus and act independently, i.e. transmit data directly to RAM system memory; Such devices are called tires leading (Bus Masters). Theoretically, the processor simultaneously with data transmissions by bus can be performed by another job; In practice, the situation is complicated by several factors. For proper implementation mastering tires (Bus Mastering) requires arbitration of tire query, which is provided with a chipset. Tire mastering is also called "First Party" DMA, since the work is managing the device performing the transmission.

Now tire mastering is implemented on the PCI bus; Added also support for hard disks IDE / ATA implementation of tire masting on PCI under certain conditions.

Principle of local tire

The beginning of the 90s is characterized by the transition from text applications to the graphic and increasing popularity of the Windows operating system. And this led to a huge increase in the amount of information that should be transmitted between the processor, memory, video and hard drives. The standard screen monochromatic (black and white) text contains only 4000 bytes of information (2000 for characters and 2000 codes for screen attributes), and the standard 256-color Windows requires more than 300,000 bytes! Moreover, the modern resolution of 1600x1200 at 16 million colors requires 5.8 million bytes of information on the screen!

Software transition from text on schedule meant also an increase in program sizes and increased memory requirements. From the point of view of I / O to handle additional data for the video card and hard drives of huge capacitance, a much big I / O bandwidth is required. With this situation, it was necessary to encounter when the 80486 processor appears, the performance of which was much higher than the previous processors. The ISA bus has ceased to meet the increased requirements and has become a bottleneck in increasing PC performance. The increase in the speed of the processor gives little, if it should expect a slow system bus for data transmission.

The decision was found in the development of a new faster tire, which was supposed to supplement the ISA bus and apply specifically for such high-speed devices as a video card. This tire was to be placed on (or near) a much faster memory bus and work approximately with the external speed of the processor to transmit data much faster than the standard ISA bus. When placing such devices near ("locally"), the processor appeared local tire. The first local bus was VESA Local Bus (VLB), and the modern local bus in most PC is the PERIPHERAL COMPONENT InterConnect bus (PCI).

System tire

System tire (System Bus) connects the processor with the main RAM memory and, possibly, with L2 cache. It is the central bus of the computer and the remaining tires are "branched" from it. The system bus is implemented as a set of conductors on the motherboard and must comply with the specific type of processor. It is the processor that determines the characteristics of the system tire. At the same time, the faster the system bus, the faster the remaining electronic components of the PC should be.

|

Consider the RS system tires with multiple generation processors. In the processors of the first, second and third generations, the frequency of the system tire was determined by the processor operating frequency. As the processor speed increases, the speed of the system tire increased. At the same time, the address space increased: in 8088/8086 processors, it was 1 MB (20-bit address), in the 80286 processor the address space was increased to 16 MB (24-bit address), and from the processor 80386, the address space is 4 GB (32 -bit address).

|

As can be seen from the table for the fourth-generation processors, the speed of the system tire first corresponded to the operating frequency of the processor. However, technological advances made it possible to increase the frequency of the processor, and the correspondence of the speed of the system tire required an increase in the speed of external components, mainly system memory, which was associated with significant difficulties and cost limits. Therefore, in the 80486DX2-50 processor was first used doubling frequency CLOCK DOUBLING: The processor worked with internal 50 MHz synchronization frequency, and exterior The speed of the system tire was 25 MHz, i.e. Only half of the operating frequency of the processor. This reception significantly improves the performance of the computer, especially due to the presence of an internal L1 cache, which satisfies most processor handlers to system memory. Since multiplication of frequency (Clock Multiplying) has become a standard way to improve computer performance and is used in all modern processors, and the frequency multiplier is adjusted to 8, 10 or more.

|

For a long time, the PC system tires with the processors of the fifth generation worked at a speed of 60 MHz and 66 MHz. A significant step forward was to increase the data width to 64 bits and expand the address space to 64 GB (36-bit address).

The speed of the system tire was raised to 100 MHz in 1998 due to the development of the PC100 SDRAM chip. RDRAM memory microcircuits allow you to further increase the speed of the system tire. However, the transition from 66 MHz to 100 MHz has provided a significant impact on processors and motherboards with Socket 7. In the Pentium II modules up to 70-80% of traffic (information transmissions), is carried out inside the new SEC cartridge (Single Edge Cartridge) in which the processor and Both L1 cache cache and L2-cache. This cartridge works with its speed, independent of the speed of the system tire.

|

The I820 and I815 chipsets developed for the Pentium III processor are designed for a 133 MHz system bus. Finally, in the AMD Athlon processor, significant changes were introduced into the architecture and the concept of the system tire turned out to be unnecessary. This processor can work with different RAM types at a maximum frequency of 200 MHz.

Types of I / O Tires

In this section, we will discuss the various I / O tires, and most of it is dedicated to modern tires. The overall view of the use of I / O bus gives the following figure, clearly showing the purpose of various I / O tes of the modern PC.

The following table summarizes the total information about the various I / O tires that are used in modern PC:

| Tire | Year | Width | Speed | Max. Pass ability |

| PC and XT. | 1980-82 | 8 bits | Simultaneous: 4.77-6 MHz | 4-6 MB / s |

| ISA (AT) | 1984 | 16 bits | Simultaneous: 8-10 MHz | 8 MB / s |

| MCA. | 1987 | 32 bits | Asynchronous: 10.33 MHz | 40 MB / s |

| EISA (for servers) | 1988 | 32 bits | Synchronous: Max. 8 MHz | 32 MB / s |

| VLB, for 486 | 1993 | 32 bits | Simultaneous: 33-50 MHz | 100-160 MB / s |

| PCI | 1993 | 32/64 bita | Asynchronous: 33 MHz | 132 MB / s |

| USB | 1996 | Consistent | 1.2 MB / s | |

| FireWire (IEEE1394) | 1999 | Consistent | 80 MB / s | |

| USB 2.0 | 2001 | Consistent | 12-40 MB / s |

Old tires

New modern tire PCI. And the AGP port "was born" from old tires, which can still be found in the PC. Moreover, the oldest Tire of ISA is still used even in the newest RS. Next, we consider several more old RS tires.

Industry Standard Architecture Tire (ISA)

This is the most common and truly standard tire for PC, which is used even in newest computers Despite the fact that it has practically not changed since its expansion up to 16 bits in 1984. Of course, it is now supplemented with faster tires, but "survivors" due to the presence of a huge database of peripheral equipment designed for this standard. In addition, there are many devices for which the ISA speeds are more than enough, for example for modems. According to some experts to the "dying", the ISA tire will take place at least 5-6 years.

The width and speed of the ISA bus determined by the processors with which she worked in the first PC. The original ISA bus in IBM PC had 8 bits width, corresponding to 8 bits of the external processor data tire 8088, and worked at a frequency of 4.77 MHz, which also corresponds to the processor speed of 8088. In 1984, the IBM AT computer appeared with the 80286 processor and the width of the tire was doubled Up to 16 bits, as in the external data tire of the processor 80286. At the same time, up to 8 MHz tire speed was raised, which also corresponded to the processor speed. Theoretically, the tire throughput is 8 MB / s, but almost it does not exceed 1-2 MB / s.

In modern RS, the ISA bus acts as inner tireused for keyboard, flexible disk, consecutive and parallel ports, and how external expansion tireTo which 16-bit adapters can be connected, such as a sound card.

Subsequently, the AT processors have become faster, and then their data bus has been increased, but now the requirement of compatibility with existing devices caused manufacturers to adhere to the standard and the ISA bus from that time practically did not change. The ISA bus provides sufficient bandwidth for slow devices and probably guarantees compatibility with almost every RS released.

Many extension cards, even modern, are still 8-bit (you can learn about the map connector - 8-bit cards are used only the first part of the ISA connector, and the 16-bit cards use both parts). For these cards, the low bandwidth of the ISA bus does not play roles. However, access to interrupts from IRQ 9 to IRQ 15 is provided through the conductors in the 16-bit part of the tire connectors. That is why most modems cannot be connected to IRQ with large numbers. IRQ lines between ISA devices cannot be divided.

Document THE PC99 SYSTEM DESIGN GUIDEprepared by Intel and Microsoft companies categorically requires the removal of ISA tire slots from motherboards, so you can expect that the days of this "deserved" tire are considered.

MicroChannel Architecture tire (MCA)

This tire has become an IBM attempt to make an ISA tire "more and better." When the 80386DX processor appears in the mid-80s, the IBM has decided to develop a bus that corresponds to such a data width. The MCA bus had a 32-bit width and had several advantages compared to the ISA bus.

The MCA tire had several excellent opportunities, taking into account the fact that it appeared in 1987, i.e. Seven years before the PCI tire appears with similar capabilities. In some respects, Msa Shina is simply ahead of his time:

- 32 Bit width: The tire has a 32-bit width, like the local tires VESA and PCI. Its bandwidth was much higher compared to the ISA bus.

- Tire mastering: The MCA bus effectively supported tire adapters, including the correct bire arbitration.

- The MCA bus automatically configured the adapter cards, so the jumpers became unnecessary. This happened 8 years before Windows 95 has turned PNP technology into a generally accepted for PC.

The MCA tire had huge potential. Unfortunately, IBM adopted two such solutions that did not contribute to the spread of this tire. First, the MES tire was incompatible with the ISA bus, i.e. The ISA cards did not work at all in the PC from the MES bus, and the computer market is very sensitive to the backward compatibility problem. Secondly, IBM decided to make the MSA bus with his property, without selling a license for its application.

These two factors together with a higher cost of systems with a bus of MES led to the obligation of the MSA tire. Since PS / 2 computers are no longer produced, the MSA bus "died" for the RS market, although IBM still uses it in its RISC 6000 UNIX servers. The history of the MES bus is one of the classic examples of how non-technical questions in the world of computers are often dominated by technical.

Bus Extended Industry Standard Architecture (EISA)

This tire has never become such a standard, which is the ISA bus, and not gained widespread. In fact, she was the answer to Compaq on the MSA tire and led to similar results.

Compaq When developing the EISA bus, avoid two major IBM errors. First, the EISA tire was compatible with the ISA bus and, secondly, it was allowed to use it to all PC manufacturers. In general, the EISA tire had significant technical advantages Over the ISA bus, but the market did not perceive it. The main features of the EISA tire:

- Compatibility with the ISA bus: ISA cards could work in EISA slots.

- Tire width 32 bits: Bus width increased to 32 bits.

- Tire mastering: EISA bus effectively supported tire adapters, including the correct bus arbitration.

- Plug and Play Technology (PNP): EISA bus automatically configured adapter cards similarly to the PNP standard of modern systems.

EISA-based systems are sometimes found in network file servers, and in desktop RS, it does not apply due to higher cost and lack of a wide selection of adapters. Finally, the bandwidth is significantly inferior to the VESA Local Bus and PCI local bus. Almost tire now EISA is close to "dying".

Tire VESA Local Bus (VLB)

The first is quite popular local tire VESA Local Bus (VL-BUS or VLB) appeared in 1992. Abbreviation VESA means Video Electronics Standards Association, and this association was created in the late 80s to solve the problems of video systems in the PC. The main reason for the development of the VLB bus was the improvement of the performance of the RS video system.

The VLB bus is a 32-bit bus that is a direct extension of the processor 486 memory bus. VLB tire slot is a 16-bit ISA slot with added at the end of the third and fourth connectors. The VLB bus typically operates at 33 MHz, although high speed is also possible in some systems. Since it is an extension of the ISA bus, an ISA card can be used in the VLB slot, but it makes sense at the beginning to take ordinary ISA slots and leave a small number of VLB slots for VLB cards, which, of course, do not work in ISA slots. The use of a VLB video card and an I / O controller significantly improves the system performance compared to a system that has only one ISA bus.

Despite the fact that the VLB bus was very popular in the PC with the processor 486, the appearance of the PENTIUM processor and its local Tire PCI in 1994 led to a gradual "obligation" VLB tires. One of the reasons for this was the effort of Intel to promote the PCI bus, but it was somewhat technical problemsassociated with the implementation of VLB. First, the tire design is very "tied to the processor 486, and the transition to Pentium caused compatibility issues and other problems. Secondly, the tire itself had technical disadvantages: a small number of cards on the tire (often two or even one), synchronization problems when using multiple cards and the lack of support for mastering tires and Plug and Play technology.

Now the VLB bus is considered outdated and even in the last motherboards with the processor 486, the PCI bus is used, and with PENTIUM processors - only PCI. However, the PC with the VLB bus is inexpensive and sometimes you can still meet them.

PERIPHERAL COMPONENT INTERCONNECT (PCI) tire

The most popular I / O bus interaction of peripheral components PERIPHERAL COMPONENT INTERCONNECT - PCI) was developed by Intel in 1993. It was focused on the fifth and sixth generation systems, but was also applied in the last generation of motherboards with the processor 486.

Like the VESA Local Bus tire, the PCI bus has a 32 bits width and usually operates at 33 MHz. The main advantage of PCI over the VESA Local Bus tire lies in the chipset that runs the bus. The PCI bus is controlled by special schemes in the chipset, and the VLB bus was, mostly, simply extending the processor 486 bus. The PCI bus in this regard is not "tied" to the processor 486 and its chipset provides the right bus control and bus arbitration, allowing PCI to do much more What could VLB bus. The PCI bus is also used outside the PC platform, providing versatility and reducing system development costs.

In modern RS, the PCI bus acts as inner tirewhich connects to the EIDE channel on the motherboard and how external expansion tirewhich has 3-4 expansion slots for PCI adapters.

In modern RS, the PCI bus acts as inner tirewhich connects to the EIDE channel on the motherboard and how external expansion tirewhich has 3-4 expansion slots for PCI adapters.

The PCI bus is connected to the system bus through a special "bridge" (Bridge) and operates at a fixed frequency, regardless of the processor synchronization frequency. It is limited to five expansion slots, but each of them can be replaced by two devices built into the motherboard. The processor can also support several bridge chips. The PCI bus is more strictly specified compared to the VL-BUS bus and provides several additional features. In particular, it supports cards having a supply voltage +3.3 V and 5 V using special keys that do not allow insert a map into an inappropriate slot. Next, the functioning of the PCI tire is considered in more detail.

PCI tire performance

The PCI bus actually has the greatest performance among the total I / O tires in modern RS. This is explained by several factors:

- Batch mode (BURST MODE): The PCI bus can transmit information in packet mode when it is possible to transmit multiple data sets after the initial addressing. This mode is similar to cache packing (Cache Bursting).

- Tire mastering: The PCI bus supports full mastering, which helps increase productivity.

- High bandwidth options: Version 2.1 PCI Tire Specifications Adjusts to 64 bits and 66 MHz, which increases current performance four times. In practice, the 64-bit Tire PCI is not yet implemented in the PC (although it is already applied in some servers) and the speed is now limited to 33 MHz, mainly due to compatibility issues. For a while you will have to be limited to 32 bits and 33 MHz. However, thanks to AGP in a somewhat modified form, higher performance will be implemented.

The PCI bus speed depending on the chipset and motherboard can be installed as synchronous or asynchronous. When synchronous configuration (used in most PC), the PCI bus works with half the speed of the memory bus; Since the memory bus usually works for 50, 60 or 66 MHz, the PCI bus operates at a frequency of 25, 30 or 33 MHz. When asynchronous tuning, the PCI bus speed can be set independently of the speed of the memory bus. This is usually controlled by jumpers on the motherboard or BIOS parameters. "Overclocking) of the System Bus in the PC, which uses the PCI synchronous bus, will cause" acceleration "and PCI peripheral devices, often causing the problems of the unstable operation of the system.

In the initial implementation of the PCI bus worked at 33 MHz, and the subsequent PCI 2.1 specification determined the frequency of 66 MHz, which corresponds to the bandwidth of 266 MB / s. The PCI bus can be configured to the width of data 32 and 64 bits and 32- and 64-bit cards are allowed, as well as separated interrupts, which is convenient in high-performance systems in which IRQ lines are not enough. From mid-1995, all high-speed RS devices interact with each other through the PCI bus. Most often it is used for hard drive controllers and graphic controllers, which are mounted directly on the motherboard or on expansion cards in the PCI bus slots.

PCI bus expansion slots

The PCI bus allows more expansion slots than the VLB bus, without causing technical problems. Most systems with PCI are supported by 3 or 4 PCI slots, and some are significantly larger.

Note: In some systems, not all slots ensure tire mastering. Now it meets less often, but still it is recommended to see the motherboard manual.

The PCI bus allows a greater variety of expansion cards compared to the VLB bus. Most often there are video cards, SCSI host adapters and high-speed network cards. (Hard drives also work on the PCI bus, but they are usually connected directly to the motherboard.) However, we note that the PCI bus does not implement some functions, for example, sequential and parallel ports should remain on the ISA bus. Fortunately, even now the ISA bus remains more than sufficient for these devices.

PCI Tire Interrupts

The PCI bus uses its internal interrupt system to handle requests from cards on the bus. These interrupts are often called "#a", "#B", "#C" and "#d" to avoid confusion with usually numbered system IRQ, although sometimes they are also called from "# 1" to "# 4". These interrupt levels are usually invisible to the user with the exception of the BIOS BIOS settings screen for PCI, where they can be used to control the operation of PCI cards.

These interrupts, if they are required to the cards in slots, are displayed on conventional interrupts, most often on IRQ9 - IRQ12. PCI slots in most systems can be displayed on most of the four conventional IRQs. In systems with more than four PCI slots or having four slots and the USB controller (which uses PCI), two or more PCI devices are separated by IRQ.

Mastering Tire PCI.

Recall that bus mastering is the ability of devices on the PCI tire (different, of course, from the system chipset) to control the bus and directly perform transmissions. The PCI bus has become the first bus tire, which led to the popularity of tire mastering (probably because operating system And programs were able to use its advantages).

The PCI bus supports complete tire mastering and provides tire arbitration tools through a system chipset. The PCI design allows simultaneous mastering bus of several devices, and the arbitration scheme ensures that no device on the bus (including processor!) Does not block any other device. However, it is allowed to use the total bandwidth of the tire, if other devices do not pass anything. In other words, the PCI bus acts as a tiny the local network Inside the computer in which several devices can interact with each other, sharing the communication channel, and which controls the chipset.

Plug and Play Technology for PCI Tire

The PCI bus is part of the Plug and Play (PNP) standard developed by Intel, Microsoft and many others. PCI bus systems first popularized PNP application. The PCI chipset circuits control the identification of maps and together with the operating system and BIOS automatically produce resource allocation for compatible cards.

The PCI bus is constantly improving and developing is managed by the PCI Special Interest Group, which includes Intel, IBM, Apple, etc. The result of these developments has increased tire frequency up to 66 MHz and expanding data up to 64 bits. However, I. alternative options, for example, an accelerated graphic port (AGP) and a high-speed serial FireWire tire (IEEE 1394). In fact, AGP is a PCI bus 66 MHz (version 2.1), which introduced some improvements focused on graphic systems.

Another initiative is a tire PCI-X.Also called "Project One" and "Future I / O". IBM, Mylex, 3Com, Adaptec, Hewlett-Packard and Compaq want to develop a special high-speed PCI bus version. This tire will have 1 GB / s bandwidth (64 bits, 133 MHz). Intel and Dell Computer are not involved in this project.

Dell Computer, Hitachi, Nec, Siemens, Sun Microsystems and Intel in response to Project One made a Next-Generation I / O bus development initiative ( NGIO.) Focused on the new I / O architecture for servers.

In August 1999, seven leading companies (COMPAQ, Dell, Hewlett-Packard, IBM, Intel, Microsoft, Sun Microsystems) announced their intention to combine the best ideas of Future I / O and Next Generation I / O. A new open I / O architecture for servers must provide bandwidth up to 6 GB / s. It is expected that the new NGIO standard will be adopted at the end of 2001.

Accelerated graphic port

The need to increase bandwidth between the processor and the video system first led to the development of a local I / O bus, starting with VESA Local Bus and ending with a modern PCI bus. This trend continues, and the requirement of increased bandwidth for video does not even satisfy the PCI bus with its standard bandwidth of 132 MB / s. Three-dimensional graphics (3D Graphics) allows you to simulate virtual and real worlds on the screen with the smallest items. Displaying textures and hiding objects require huge amounts of data and a video card must have quick access to these data to maintain a high frequency of regeneration.

Traffic on the PCI bus becomes very tense in modern RS, when video, hard drives and other peripheral devices compete with each other by the only I / O bandwidth. To prevent PCI bus saturation video information, Intel has developed a new interface specifically for the video system, which is called accelerated graphic port ACCELATED Graphics Port - AGP).

The AGP port is designed in response to the requirement of increasingly productivity for the video. As the programs and computers such as three-dimensional acceleration and playback of video films (Full-Motion Video Playback), the processor and video chipset must process more and more information. In such applications, the PCI bus has reached its limit, all the more so that it also uses hard drives and other peripheral devices.

In addition, more and more video memory is required. For three-dimensional graphics, you need more memory and not only for the screen image, but also for the production of calculations. Traditionally, this problem is solved by placing more and more memory on the video card, but there are two problems:

- Cost: Video memory more expensive RAM memory.

- Limited capacity: The memory capacity on the video card is limited: if you place 6 MB on the map and 4 MB is required for the frame buffer, then only 2 MB remains for processing. It is not easy to expand this memory and cannot be used for something else if the video processing is not needed.

AGP solves these problems allowing the video processor to access the main system memory for the production of calculations. This technique is much more efficient, since this memory can be dynamically divided between system processor and the video processor depending on the needs of the system.

The idea of \u200b\u200bimplementing AGP is quite simple: Create a fast specialized interface between a video chipset and a system processor. The interface is implemented only between these two devices, which provides three main advantages: it is easier to implement the port, it is easier to increase the speed of AGP and can be entered into an interface specific to video improvements. AGP chipset acts as an intermediary between the processor, L2-cache Pentium II, system memory, video card and PCI bus, implementing the so-called quad port (Quad Port).

AGP is considered a port, not a tire, as it combines only two devices (processor and video card) and does not allow expansion. One of the main advantages of AGP is that it isolates the video system from the rest of the PC components, excluding competition for the bandwidth. Since the video card is removed from the PCI bus, the remaining devices can work faster. For AGP on the motherboard there is a special socket, which is similar to the PCI bus socket, but is placed elsewhere. The following figure from above shows two ISA tire sockets (black), then two PCI tire sockets (white) and ADP socket (brown).

AGP appeared at the end of 1997 and its first supported the 440LX Pentium II chipset. Next year, AGP chipsets of other companies appeared. For details on AGP see site http://developer.intel.com/technology/agp/.

AGP interface

The AGP interface in many respects is similar to the PCI bus. The slot itself has the same physical shapes and sizes, but shifted from the edge of the motherboard further than the PCI slots. The AGP specification is actually based on the PCI 2.1 specification, which allows 66 MHz speed, but this speed is not implemented in the PC. AGP motherboards have one expansion slot for AGP video card and one PCI slot is less, and the rest are similar to PCI motherboards.

Width, speed and bandwidth

The AGP bus has a 32-bit width, like the PCI bus, but instead of working with half the speed of the memory bus, as PCI does, it works at full speed. For example, on the standard Pentium II motherboard, the AGP bus runs 66 MHz instead of 33 MHz PCI bus. It immediately doubles the port of bandwidth - instead of a limit of 132 MB / s for PCI port AGP has in the lowest speed of a strip of 264 MB / s. In addition, it does not share the strip with other PCI bus devices.

In addition to doubling the speed of the tire in AGP, mode is defined 2x.which uses special signals that allow you to transfer multiple data through the port at the same synchronization frequency. In this mode, the information is transmitted by the increasing and falling fronts of the synchronization signal. If the PCI bus transfers only one front data, AGP transmits data on both fronts. As a result, the performance is still doubled and theoretically reaches 528 MB / s. It is also planned to implement mode 4x.in which there are four transmissions in each synchronization cycle, which will increase the performance up to 1056 MB / s.

Of course, all this is impressive for the video card, the bandwidth of 1 GB / s is very good, but one problem arises: in modern PC there are several tires. Recall that in the processors of the Pentium class data width of 64 bits and it runs 66 MHz, which provides the theoretical bandwidth of 524 MB / s, so the band in 1 GB / s does not give a significant gain, if not to increase the speed of the data bus over 66 MHz . In the new motherboards, the speed of the system tire is increased to 100 MHz, which increases throughput up to 800 MB / s, but this is not enough to meet the transmission of the mode 4x..

In addition, the processor should access the system memory, and not just a video system. If the entire system strip is 524 MB / s busy video through AGP, what remains to do the processor? In this case, the transition to the system speed of 100 MHz will give a certain win.

AGP port video conveyorization

One of the advantages of AGP is the ability to conize data requests. Conveyorization was first used in modern processors as a way to improve productivity due to overlapping consecutive fragments of tasks. Thanks to AGP, a video chipset can use a similar reception when requesting information from memory, which significantly improves performance.

AGP access to system memory

The most important feature of AGP is the ability to divide the basic system memory with a video chipset. This provides a video system access to greater memory for the implementation of three-dimensional graphics and other processing, without requiring a large video memory on the video card. The memory on the video card is divided between the frame buffer (Frame Buffer) and other applications. Since the frame buffer requires a high-speed and expensive memory, such as VRAM, in most cards all Memory is performed on the VRAM, although this is required for memory areas except the frame buffer.

Note that AGP not Refers to a unified memory architecture (UNIFIED Memory Architecture - UMA). In this architecture all The video card memory, including the frame buffer, is taken from the main system memory. In AGP, the frame buffer remains on the video card, where it is located. The frame buffer is the most important component of the video memory and requires the highest performance, therefore it is more expedient to leave it on the video card and use VRAM for it.

AGP allows the video processor to access the system memory to solve other tasks requiring memory, such as texturing and other three-dimensional graphics operations. This memory is not so critical as a frame buffer, which allows you to reduce the video card by reducing the VRAM memory capacity. Reference to system memory is called direct execution from memory Direct Memory Execute - Dime). Special device called graphic Aperture Transaction Table (Graphics Aperture Remapping Table - Gart), operates with RAM addresses in such a way that they can be distributed in system memory with small blocks, and not one large section, and provides their video card as part of the video memory. A visual view of the AGP functions gives the following drawing:

Requirements AGP.

To use in the AGP system, you must perform several requirements:

- The presence of AGP video card: This requirement is quite obvious.

- The presence of motherboard with the AGP chipset: Of course, the chipset on the motherboard must support AGP.

- Operating system support: The operating system must support the new interface using its internal drivers and procedures.

- Driver support: Of course, the video card requires special drivers to support AGP and use its special features, such as mode 3X..

New serial tires

For 20 years, many peripheral devices have been connected to the same parallel and sequential ports that appeared in the first PC, and with the exception of the Plug and Play standard "I / O technology" has changed little from 1081. However, by the end of the 90s of the last century, users even stronger feel the limitations of standard parallel and serial ports:

- Bandwidth: Serial ports have the maximum bandwidth 115.2 Kb / s, and parallel ports (depending on the type) of about 500 kb / s. However, for devices such as digital video cameras, a significantly higher bandwidth is required.

- Easy use: Connect devices to the old ports is very uncomfortable, especially through the transition connectors of parallel ports. In addition, all ports are located behind the PC.

- Hardware resources: For each port requires its IRQ line. The RS has only 16 IRQ lines, most of which are already occupied. Some PCs for connecting new devices have only five IRQ lines.

- Limited number of ports: Many PCs have two consecutive Som ports and one parallel LPT port. It is allowed to add more ports but by using valuable IRQ lines.

In recent years, I / O technology has become one of the most dynamic areas of the development of desktop RS and two developed data transmission standards strongly changed the ways to connect peripheral devices and raised the concept of Plug and Play to a new height. Thanks to the new standards, any user will be able to connect to the PC almost unlimited multiple devices literally in a few seconds without having special technical knowledge.

Universal sequential tire

Developed by COMPAQ, Digital, IBM, Intel, Microsoft, NEC and Northern Telecom universal sequential tire Universal Serial Bus - USB provides a new connector for connecting all common I / O devices, eliminating a variety of modern ports and connectors.

USB bus allows connecting up to 127 devices using purchase compound (Daisy-chaning) or use USB-huba (USB HUB). Hub himself, or ConcentratorIt has several sockets and inserted into a PC or another device. Seven peripheral devices can be connected to each USB hub. Among them, there may be a second hub to which one more seven peripheral devices can be connected, etc. Together with the data signals, the USB bus transfers and the supply voltage is +5V, so small devices, for example, manual scanners may not have their own power supply.

The devices are connected directly to a 4-pin socket (socket) on a PC or a hub in the form of a rectangular socket of type A. All cables that are constantly connected to the device have a plug of type A. Devices that use a separate cable, have a square coat of type B, and The cable that connects them has a plug of type A or type V.

The USB bus removes the limitations of the serial ports on the UART database. It works at a speed of 12 MB / s, which corresponds to network technologies Ethernet and Token Ring and provides sufficient bandwidth for all modern peripheral devices. For example, USB bus bandwidth is sufficient to support devices such as external cD-ROM drives and ribbon drives, as well as ISDN interfaces of regular phones. It is also sufficient to transmit digital audio signals directly in the speakers equipped with a digital analog converter, which eliminates the need to have a sound card. However, the USB bus is not intended to replace the network. To obtain an acceptable low cost, the distance between devices is limited to 5 m. For slow devices type of keyboard and mouse, you can set the data rate of 1.5 MB / s, saving bandwidth for faster devices.

The USB bus fully supports Plug and Play technology. It eliminates the need to install expansion cards inside PC and subsequent reconfiguration of the system. The bus allows you to connect, configure, use and, if necessary, disconnect the peripheral devices at a time when the PC and other devices work. You do not need to install drivers, select sequential and parallel ports, as well as define IRQ, DMA channels and I / O addresses. All this is achieved by controlling the peripheral devices using the host controller on the motherboard or on the PCI map. The host controller and subordinate controllers in the hubs are controlled by peripheral devices, reducing the load on the processor and increasing the overall performance of the system. The host controller itself manages system software as part of the operating system.

The data is transmitted by a bidirectional channel that control the host controller and subordinate hub controllers. Superior tire mastering allows you to constantly reserve for specific peripherals part of the total bandwidth; This method is called isochronous data transmission (ISOCHRONOUS DATA TRANSFER). The USB bus interface contains two main modules: serial interface machine (Serial Interface Engine - Sie), which is responsible for the protocol of the tire, and root hub (Root Hub) used to extend the number of USB bus ports.

USB bus highlights each port 500 mA. Due to this, low-power devices that usually require a separate AC transducer (AC Adapter), you can feed via cable - USB allows the PC to automatically determine the required power and deliver it to the device. Hubs allow full power from the USB tire (BUS Powered), but can have their own AC converter. Hubs with private food providing 500 mA per port provide maximum flexibility for future devices. Hubes with port switching isolate all ports from each other, so one "shortened" does not violate the work of others.

USB bus promises the creation of a PC with the only uSB port Instead of modern four or five different connectors. One large powerful device can be connected to it, such as a monitor or printer that will act as a hub, providing connecting other smaller devices, such as mouse, keyboard, modem, scanner, digital chamber, etc. However, this will require the development of special device drivers. However, this configuration of the PC has disadvantages. Some experts believe that the USB architecture is rather complicated, and the need to support many different peripheral devices requires the development of a whole set of protocols. Others believe that the hub principle simply displays the cost and complexity from the system unit to the keyboard or monitor. But the main obstacle to USB's success is the IEEE 1394 FireWire standard.

IEEE 1394 Firewire bus

This high-speed peripheral tire standard is designed by Apple Computer, Texas Instruments and Sony. It was developed as a USB bus complement, and not as an alternative to it, since both tires can be used in one system, similar to modern parallel and serial ports. However, large manufacturers of digital cameras and printers are interested in the IEEE 1394 bus more than in the USB bus, because for digital cameras, the socket 1394 is best suited, and not a USB port.The IEEE 1394 bus (commonly called FireWire - the "fiery wire") is largely similar to the USB bus, also being a serial tire with a hot substitution, but much faster. In IEEE 1394 there are two levels of the interface: one for the tire on the computer's motherboard and the second for the point-to-point interface between the peripheral device and the computer over the serial cable. A simple bridge combines these two levels. The bus interface supports data transfer rates at 12.5, 25 or 50 MB / s, and the cable interface is 100, 200 and 400 MB / s, which is much larger than the speed of the USB bus - 1.5 MB / s or 12 MB / s. The 1394B specification determines other ways of encoding and transmitting data, which allows you to increase the speed of up to 800 MB / s, 1.6 GB / s and more. Such high speed allows you to apply IEEE 1394 to connect to PC of digital cameras, printers, televisions, network cards and external storage devices.

The IEEE 1394 cable connectors are made so that the electrical contacts are inside the connector body, which prevents the use of electrical shock of the user and contamination of the contacts by the user's hands. These small and convenient connectors are similar to the Nintendo Gameboy gaming connector, which showed excellent durability. In addition, these connectors can be inserted blindly from behind the PC. No terminators are required (Terminators - Terminators) and manual installation of identifiers.

The IEEE 1394 bus is designed for a 6-wire cable up to 4.5 m long, which contains two pairs of conductors for data transmission and one pair to power the device. Each signal pair is shielded and the entire cable is also shielded. The cable allows voltage from 8 V to 400 V and current to 1.5 A and saves the physical continuity of the device when the device is turned off or defective (which is very important for the serial topology). The cable provides power to the devices connected to the bus. As the standard improves, the tire is expected to provide long distances without repeaters and even greater bandwidth.

The basis of any IEEE 1394 compound serves as a physical layer and communication level chip, and two chips are needed for the device. The physical interface (PHY) of one device is connected to the phy of another device. It contains the schemes necessary to perform the functions of arbitration and initialization. The communication interface connects PHY, as well as internal device circuits. It transmits and accepts IEEE 1394 packets and supports asynchronous or isochronous data transmission. The ability to support asynchronous and isochronous formats in the same interface allows you to work on a non-critical bus tire for applications, such as scanners or printers, as well as real-time applications, such as video and sound. All physical-level chips use the same technology, and the communication level chips are specific for each device. This approach allows the IEEE 1394 bus to act as a "node" system (Peer-Peer), in contrast to the client-server approach in the USB bus. As a result, the IEEE 1394 system does not require a service host, nor PC.

Asynchronous transmission is a conventional data transmission between computers and peripheral devices. Here, the data is transmitted in one direction and are accompanied by a subsequent confirmation of the source. In asynchronous data transmission, the emphasis is made on delivery, and not to productivity. Data transfer is guaranteed and reconnaissance (Retries). Isochronous data transmission provides a stream of data at a predetermined speed, so the application can process them with temporary ratios. This is especially important for multimedia data critical when delivery is exactly in time (Just-in-Time Delivery) eliminates the need for expensive buffering. Isochronous data transmission operates on the basis of a wide broadcast (Broadcast), when one or more devices can "listen" (LISTEN) transmitted data. By the IEEE 1394 bus, you can simultaneously transmit several channels (up to 63) of isochrona data. Since isochronous transmissions can occupy a maximum of 80% of the bus bandwidth, there is a sufficient bandwidth and for additional asynchronous transmissions.

Scalable IEEE 1394 tire architecture and flexible topology make it ideal for connecting high-speed devices: from computers and hard drives to digital audio and video equipment. Devices can be connected in the form of a loop or tree topology. Figure On The left shows two separate working areas connected by the IEEE Tire Bridge 1394. The working area # 1 consists of a camcorder, PC and VCR, which are all connected via IEEE 1394. PC is also connected to a physically remote printer through a repeater 1394, which increases the distance between devices, Enhance tire signals. The IEEE 1394 bus is allowed to 16 "jumps" (HOPS) between any two devices. Splitter (Splitter) 1394 is used between the bridge and the printer to provide another port for connecting the IEEE 1394 bus bridge. Motors provide for users a greater flexibility of the topology.

The # 2 workspace contains on the 1394 bus segment only RS and printer, as well as a connection with the bus bridge. Bridge isolates data traffic inside each workspace. The IEEE 1394 bus bridges allow you to transmit selected data from one bus segment to another. Therefore, PC # 2 can request images from a video recorder in the working area # 1. Since the tire cable transmits and power the PHY signal interface is always with power and data is transmitted even if PC # 1 is turned off.

Each IEEE 1394 bus segment allows connecting to 63 devices. Now each device may be up to 4.5 m; Large distances are possible both with repeaters, and without them. Enhancements of cables will allow you to cut devices over long distances. With the help of bridges, you can combine more than 1000 segments, which ensures significant potential for expansion. Another advantage consists in the ability to perform transactions with different speeds by one media for the device. For example, some devices can operate at a speed of 100 MB / s, and others - with a speed of 200 MB / s and 400 MB / s. It is allowed hot replacement (connection or disabling devices) on the bus even when the tire is fully running. Automatically recognize changes in the topology of the tire. This makes unnecessary address switches and other user interventions for tire reconfiguration.

Thanks to the technology of transferring packets, the IEEE 1394 bus can be organized as if the memory space is distributed between devices, or as if the devices are in the slots on the motherboard. The address of the device consists of 64 bits, and 10 bits are discharged for network identifier, 6 bits for the node identifier and 48 bits for memory addresses. As a result, you can add 1023 networks of 63 nodes, each has a memory of 281 TB. Memory addressing, not channels, considers resources by registers or memory to which you can contact the processor-memory transaction. All this provides a simple network organization; For example, a digital camera can easily transfer images directly to a digital printer without an intermediary. The IEEE 1394 bus shows that RS loses its dominant role to combine the medium and can be considered a very intelligent node.

The need to use two chips instead of one makes peripheral devices for the IEEE 1394 bus more expensive compared to devices for SCSI, IDE or USB, so it is not suitable for slow devices. However, its advantages for high-speed applications, such as digital video transfers, turns the IEEE 1394 bus to the main interface for consumer electronics.

Despite the advantages of the IEEE 1394 tires and the appearance of motherboards with embedded controllers of this tire in 2000, the future success of FireWire is not guaranteed. The appearance of the USB 2.0 specification has complicated the situation.

USB 2.0 specification

In the development of this specification focused on supporting high-speed peripheral devices, COMPAQ, Hewlett-Packard, Intel, Lucentt-Packard, Intel, Lucentt-Microsoft, Nec and Philips took part. In February 1999, it was announced an increase in existing productivity at 10 to 20 times, and in September 1999, according to the results of engineering research, the estimates were increased to 30 - 40 times compared with USB 1.1. There were concerns that with such a USB tire performance forever "bury" the IEEE 1394 tire. However, in general, these two tires are focused on various applications. The purpose of USB 2.0 is to provide support for all modern and future popular PC peripheral devices, and the IEEE 1394 bus is focused on connecting household audio and video devices, such as digital video recorders, DVDs and digital TVs.

According to USB 2.0, bandwidth rises from 12 MB / s to 360-480 MB / s. The USB 2.0 bus is expected to be compatible with USB 1.1, which will provide users with a painless transition to a new bus. For it, new high-speed peripheral devices will be developed, which will expand the range of PC applications. Speed \u200b\u200b12 MB / s is quite enough for devices such as phones, digital cameras, keyboard, mouse, digital joysticks, ribbon drives, drives on a flexible disk, digital speakers, scanners and printers. The increased bandwidth USB 2.0 will expand the functionality of the peripheral devices, providing support for high-resolution cameras for video conferencing, as well as high-speed scanners and next-generation printers.

Existing USB peripheral devices will work without changes in the USB 2.0 bus system. Such devices like a keyboard and mouse requires an increased USB 2.0 bandwidth and they will work as USB 1.1 devices. The increased bandwidth USB 2.0 will expand the range of peripheral devices that can be connected to the PC, and will also allow a greater number of USB devices to divide the existing bus bandwidth up to the architectural limits of the USB bus. backward compatibility USB 2.0 with USB 1.1 can be a decisive advantage in the control of the IEEE 1394 bus per interface of consumer instruments.

Standard DeviceBay.

DeviceBay. It is a new standard that is designed following the IEEE 1394 and USB tire standards. These tires allow connecting and disable devices "on the fly", i.e. During the operation of the PC. Such opportunity hot replace (Hot Swap, Hot Plug) demanded a new special connection between devices and the response to this requirement was the DeviceBay standard. It standardizes the compartments in which you can insert hard drives, CD-ROM drives and other devices. The mounting frame is installed without tools and during the operation of the PC. If the DeviceBay standard is widely distributed, it will end with flat cables inside the PC body. The entire PC can be issued as a modular design, in which all modules are connected to USB or FireWire bus as DeviceBay devices. In this case, the device can be freely moved between PC and other home appliances.

The DeviceBay standard is designed to connect such devices such as ZIP drives, CD-ROM drives, ribbon drives, modems, hard drives, PC card readers, etc.

Mikhail Tychkov Aka Hard

Good day.

If the processor is the heart of a personal computer, then tires are artery and veins for which

Electrical signals. Strictly speaking, these are communication channels used to organize interaction between devices.

Computer. By the way, if you think that the connectors where the extension boards are inserted and there are tires, then you are cruel

mistake. These are interfaces (slots, connectors), with their help connecting to tires, which, often, in general

Not visible on motherboards.

There are three main indicators of the tire work. These are clock frequency, discharge and transfer rate

data. Let's start in order.

Clock frequency

The operation of any digital computer depends on the clock frequency that determines

quartz resonator. It is a tin container in which a quartz crystal is placed. Under influence

Electric voltage in the crystal arise to electrical current oscillations. This is the most frequency of oscillations and

called clock frequency. All changes in logical signals in any computers chip occur through

Certain intervals called tactics. From here we conclude that the smallest unit of measurement of time for

Most computer logic devices have a clock or another - a period of clock frequency. Simply put - on

Each operation requires at least one clock (although some modern devices Have time to perform several operations

For one tact). Clock frequency, in relation to personal computers, is measured in MHz, where the hertz is one oscillation.

per second, respectively 1 MHz is a million oscillations per second. Theoretically, if the system bus tire of your computer

Works at a frequency of 100 MHz, it means it can perform up to 100,000,000 operations per second. By the way,

It is not at all necessary that each component of the system necessarily performed something with each tact. There are so

called empty tacts (waiting cycles) when the device is in the process of waiting for an answer from any other

Devices. For example, the operation of RAM and processor (CPU) is organized, the clock frequency of which is significantly

Above the clock frequency of RAM.

Bigness

The tire consists of several channels for transmitting electrical signals. If they say

that the tire is thirty-disconnectable, then it means that it is able to transmit electrical signals to thirty two channels

At the same time. There is one chip here. The fact is that the tire of any declared bit (8, 16, 32, 64) has, on the most

case large quantity canals. That is, if you take the same thirty-disconnect bus, then to transfer the data itself

32 channels are highlighted, and additional channels are intended for transmitting specific information.

Data transfer rate

The name of this parameter speaks for itself. It is calculated by the formula:

clock frequency * bit \u003d data rate

We will calculate the data rate for 64 discharge system bus operating on the clock frequency

at 100 MHz.

100 * 64 \u003d 6400 Mbps

6400/8 \u003d 800 MB / s

But the resulting number is not real. In life on tires affects a lot of all kinds of factors:

Inefficient conductivity of materials, interference, disadvantages of design and assembly as well as much more. By some

data, the difference between the theoretical data transfer rate and the practical can be up to 25%.

The work of each tire is monitored specifically for this designed controllers. They are part of

Set of system logic (chipset).

Now let's talk specifically about those tires that are present on the motherboard. Main

It is considered the FSB system bus (Front Side Bus). On this bus, data between the processor and the RAM is transmitted,

as well as between the processor and other personal computer devices. That's here there is one underwater stone.

The fact is that working on the material of this article, I encountered one confusion - there is such garbage like a tire

processor. According to the same data, the system bus and processor bus is the same thing, but in others - no. I rummed a bunch of books

and revised a bunch of schemes. Conclusion: At first, the processor was connected to the main system tire through its own, processor,

Tire, in the modern systems, these tires have become one whole. We say - system tire, but we mean processor, we

We say - processor tire, but mean system. Move on. Phrase: "My motherboard works at frequency

100 MHz "means that the system tire runs on a clock frequency of 100 MHz. FSB Big Damage

CPU. If you use a 64 digit processor, and the clock frequency of the system bus 100 MHz, then the data transfer rate

It will be 800 MB / sec.

In addition to the system tire on the motherboard there are still input / output tires that differ from each other

by architecture. I will list some of them:

The core of the processor is determined by the following characteristics:

- technological process;

- volume of internal cache L1 and L2;

- voltage;

- heat transfer.

Before buying a central processor, you must make sure that your chosen motherboard will be able to work with it.

It is noteworthy that one line of processors may contain a CPU equipped with different nuclei. For example, in the Intel Core I5 \u200b\u200bline, there are processors with nuclei Lynnfield, Clarkdale, Arrandale and Sandy Bridge.

What is the data tire frequency?

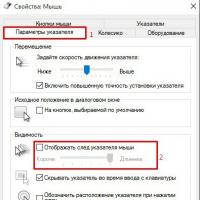

Indicator Tire frequencies data It is also indicated by Front Side Bus (or abbreviated FSB.) .

Data bus - This is a set of signal lines intended for data transmission in and of processor.

Tire frequency - This is the clock frequency with which data is exchanged between the processor and the system tire.

It should be noted that processors Apply QUAD PUMPING technology. It makes it possible to transmit 4 data blocks for one clock. The effective frequency of the tire, while increases in four. It should be remembered that for the above-marked processors, in the "Tire frequency" column indicates an increased 4 times indicator.

AMD processors Athlon 64.and Opteron. Apply Hypertransport technology, which allows the processor and RAM to carry out effective interaction. This system significantly improves overall performance.

What is the processor clock frequency?

Processor clock frequency - This is the number of processor operations per second. Under operations, in this case, the tacts are implied. The clock frequency indicator is proportional to the tire frequency (FSB).

Usually, the higher the clock frequency, the higher the performance. However, this rule works only for models of processors belonging to one line. Why? In addition to the performance of the processor, in addition to the frequency, such parameters are also influenced as:

- second-level cache size (L2);

- the presence and frequency of the third level cache (L3);

- presence of special instructions etc...

CPU clock frequency range: from 900 to 4200 MHz.

What is techprocess?

TechProcess - This is the scale of technology that determines the dimensions of the semiconductor elements constituting the database of the internal circuits of the processor. Circuits form connected transistors.

Proportional reduction in transistor dimensions, as modern technologies develop, leads to improved processor characteristics. For example, the Willamette kernel, made according to the process of 0.18 microns, possesses 42 million transistors; The prescott core with a technical process of 0.09 microns, has already 125 million transistors.

What is the magnitude of the processor heat dissipation?

Heat out - This is an indicator of the reserved power cooling system to ensure the normal functioning of the processor. The higher the value of this parameter, the stronger the processor is heated during its work.

This indicator is extremely important to consider in the event of an overestimation of the frequency of the central processor. A processor with low heat generation is cooled faster, and, accordingly, it is possible to overclock it is stronger.

It should also be borne in mind that processor manufacturers measure the heat dissipation indicator in different ways. Therefore, the comparison on this characteristic is appropriate only within the framework of the same manufacturer.

The heat generation range of the processor: from 10 to 165 W.

Support technology Virtualization Technology

Virtualization Technology. - Technology that allows one-time operation of several operating systems on one PC.

So, thanks to virtualization technology, one computer system can function as multiple virtual.

Support SSE4 technology

SSE4. - Technology that includes a package consisting of 54 new teams aimed at improving processor performance indicators during the implementation of various resource-intensive tasks.

Support SSE3 technology

SSE3. - Technology that includes a package consisting of 13 new teams. Their introduction to new generation is aimed at improving processor performance indicators in terms of data streaming operations.

Support SSE2 technology

SSE2 - technology that includes a package of commands that complement the technologies of its "predecessors": SSE and MMX. It is the development of Intel Corporation. The commands included in the set allow you to achieve a significant productivity gain in applications optimized for SSE2. This technology is supported by almost all modern processor models.

NX BIT technology support

NX BIT. - Technology capable of preventing the implementation and execution malicious code Some viruses.

Supported operational windows system XP SP2, as well as all 64-bit OS.