MCS 51 SI programming. MCS-51 microcontrollers. Structural scheme, alu, data memory. Registers of special functions

The architecture of the MCS-51 family is largely predetermined by its appointment - building compact and cheap Digital devices. All microevm functions are implemented using a single chip. The MCS-51 family includes a number of microcircuits from the simplest microcontrollers to quite complicated. MCS-51 family microcontrollers allow you to perform both control tasks of various devices and implement individual analog circuit nodes. All chips of this family work with the same mCS-51 command system , most of them are performed in the same corps with coincident Cocolevka (Numbering legs for the case). This allows you to use for the developed microcircuit devices from different firms - Maxim, Atmel, NXP, etc. (Catalog..php? Page \u003d Components_List & ID \u003d 39 "\u003e S.M. Search by parameters) without reworking the concept of device and program.

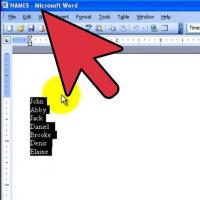

Figure 1. Structural diagram of the I8751 controller

The block diagram of the controller is presented in Figure 1. And consists of the following basic functional nodes: a control unit, an arithmetic logical device, a block of timers / counters, a serial interface block, and a program meter, data memory and program memory. Bilateral exchange is carried out using an internal 8-bit data line.

Consider a Read more assigning each block. According to such a scheme, almost all representatives of the MCS-51 family are built. The various chips of this family differ only in special purpose registers (including the number of ports). System of commands of all MCS-51 family controllers Contains 111 basic commands with a format 1, 2 or 3 bytes and does not change when moving from one chip to another. It provides excellent portability of programs from one chip to another.

Control and synchronization unit

The control and synchronization unit (Timing and Control) is designed to generate synchronizing and control signals that ensure the coordination of the joint operation of the OEEHM blocks in all allowable modes of its operation. In the composition of the control unit includes:

- - device for forming time intervals,

- - I / O logic,

- - command register,

- - electricity consumption register

- - Team decoder, computer management logic.

Team interval formation device It is intended for the formation and issuance of internal sync signals of phases, clocks and cycles. The number of machine cycles determines the time of execution of commands. Almost all OEEHM commands are performed for one or two machine cycles, except for multiplication and division commands, the duration of which is four engine cycles. Denote the frequency of the specifying generator through F G. Then the duration of the machine cycle is 12 / f g or is 12 periods of the signal of the specifying generator. I / O logic is intended for receiving and issuing signals that provide the exchange of information with external devices through the output ports of the P0-P3 output.

Register of teams Designed for recording and storing 8-bit code executable code. The operation code, using the command decoder and the computer control logic, is converted into the microprogram of the execution of the command.

Consumption Control Register (PCON) Allows you to stop the operation of the microcontroller to reduce the consumption of electricity and reduce the level of interference from the microcontroller. An even greater reduction in the consumption of electricity and the reduction of interference can be achieved by stopping the microcontroller's master generator. This can be achieved by switching a PCON consumption control system. For the option of manufacturing using N-MOP (Series 1816 or foreign microcircuits, in the name of which in the middle there is no letter "C") PCON consumption control register contains only one bit that controls the Smod serial port transmission rate, and there are no electricity consumption control bits.

Arithmetic logical device (ALU) It is a parallel eight-bit device that ensures the execution of arithmetic and logical operations. Alu consists of:

- - battery registers, TMP1 and TMP2 temporal storage registers,

- - ROM constant,

- - adder,

- - additional register (register c),

- - Battery (ACC),

- - Program State Register (PSW).

Register battery and temporary storage registers - Eight-bit registers intended for receiving and storing operands at the time of operations on them. These registers are not programmatically accessible.

ROM Constant Provides a corrective code to generate a binary-decimal data view, a mask code for bit operations and a constant code.

Parallel eight-bit adder It is a combination circuit with a sequential transfer, intended for performing arithmetic operations of addition, subtraction and logical operations of addition, multiplication, unequaveness and identity.

Register B. - The eight-bit register used during multiplication and division operations. For other instructions, it can be viewed as an additional ultraoperative register.

Battery - Eight-bit register designed to receive and storing the result obtained when performing arithmetic and logical operations or shift operations

Consecutive Interface Block and Interrupts (PIP) Designed to organize an I / O, sequential information flows and organization interrupt systems. The block includes:

- - Pip buffer,

- - control logic,

- - control register,

- - transmitter buffer,

- - receiver buffer,

- - serial port transceiver,

- - Interrupt priority register,

- - interrupt resolution register,

- - Interrupt flag processing logic and vector generation scheme.

Command Counter (Program Counter) Designed to form the current 16-bit address of the internal memory of the programs and 8/16-bit address of the external memory of the programs. The team meter includes 16-bit PC buffer, PC register and increment scheme (increasing content by 1).

Data Memory (RAM) Designed for temporary storage of information used in the program execution process.

Ports P0, P1, P2, P3 They are a quasi-documentary input ports and are intended to ensure the exchange of information of the OES with external devices, forming 32 input lines.

Timer device In the basic models of the family there are two programmable 16-bit timer / counter (T / C0 and T / C1), which can be used both as timers and as external events counters

Program State Register (PSW) Designed to store information about the state of Alu when executing the program.

Software Memory (EPROM) It is intended for storing programs and is a constant storage device (ROM). In different microcircuits apply mask ROM, washed with ultraviolet radiation or Flash. ROM.

Data pointer register (DPTR) Designed to store the 16-bit address of the external data memory or program memory.

Stack Pointer (SP) It is an eight-bit register designed to organize a special data memory (stack), in which you can temporarily save any memory check.

Microcontrollers of the MSS-51 family are built on the Harvard architecture, in which the memory of the programs and memory of these sections, have their own targeted spaces and ways to access them.

Memory program

The maximum amount of memory is 64k byte, of which 4k, 8k, 16k or 32k of the memory byte (Table 7.3.1) are located on a crystal, the remaining volume is outside the crystal.

At a voltage at the output of EA \u003d

V CC.

it is used both internal and external memory, at ea \u003d v cc \u003d 0 - only external pa-mig.

Table 7.3.1 are given addresses address access to programsfor specified cases.

The lower memory area of \u200b\u200bthe programs is returned to start the microcont-roll engine (the starting address 0000H after discharge) and under the processing of interrupts (the interrupt control is located with an 8 bytes interval: 0003H, 000BH, 0013H, etc.).

Memory programs are read only, and when handling:

Memory programs are read only, and when handling:

● K. external memorythe programs are generated ¯sen and always form a 16-bit address.

The younger address byte is transmitted through the port P0 in the first half of the machine cycle and is fixed by the ALE Gate slice in the register.

In the second half of the cycle, the P0 port is used to enter data from the external memory in the MK byte.

The senior byte of the address is transmitted through the port P2 for the entire time of memory appeals (Fig. 7.1.11);

● K. internal memorythe read signal is not formed and the cycles of the exchange in the inner tire of the microcontroller are used.

Data memory

Internal memorydata can be divided into three blocks (Table 7.3.2).  Internal memory is always addressed by the byte, which provides addresses only to 256 memory cells.

Internal memory is always addressed by the byte, which provides addresses only to 256 memory cells.

Therefore, as can be seen from Table 7.3.2, for addresses to the upper 8-bit cells of the internal RAM and registers of special functions of SFR, which occupies the same address space, in the teams are used different ways of addressing: indirect and straight.

Features of the organization of the lower region of the internal RAMreflected in Table. 7.3.3.

The younger 32 bytes of the internal RAM with addresses 00h.

1fh is grouped into the Cheat of the Bank for eight registers (R0.R7).

The following 16 bytes of RAM with addresses 20h.

2FH is an 8 × 16 \u003d 128 bit memory area that allows each separate bit to appeal.

To select the address of the Bank's register, its name R0 is used.

R7, to select a bank - Bits RS0, RS1 PSW status status register.

Addresses bits

Addresses bitsled in Table. 7.3.3.

Addressing is carried out directway.  The list of all SFR special functions registers with their addresses in Table 7.2.2.

The list of all SFR special functions registers with their addresses in Table 7.2.2.

For clarity in Table 7.3.

4 is given re-Histrow Address MapSfr.the microcircuits of the MCS-51 family.

The SFR address is determined by the set of the number of columns and lines in a hexadecimal number system.

For example, the CMOD register has the address D9H.  For SFR registers, the addresses of which will end with 0H or 8H (they are highlighted in bold), in addition to baitovaallowed beatenaddressing.

For SFR registers, the addresses of which will end with 0H or 8H (they are highlighted in bold), in addition to baitovaallowed beatenaddressing.

At the same time, the name of the bit occupying in the register N-th discharge is defined as XXH + 0NH, where XXH is the address of the register SFR, N \u003d 0.7.

Bit addresses in this region have values \u200b\u200bfrom 80H to FFH.

For example, the addresses of the battery bits ass le-zate within the E0H-E7h.

External memorydata (up to 64 KB) is created by additional memory chips connected to MK.

Special commands are used to work with the external data memory, therefore address spaces of external and internal memory do not intersect and, therefore, both types of memory mone can be used simultaneously.

To access the cells by external data memory (Fig.7.1.8):

● Commands with indirect addressing;

● read signals ¯rd and record ¯WR;

● P0 port for the transfer of the younger byte address and receiving / transmission of the data byte;

● P2 port for sending an older address byte.

Addressing methods.

The command system uses:

● Direct, indirect, register, indirectly register, direct and index addressing (indirect addressing on the amount of basic and index registers) source operands;

● Direct, register and indirectly register addressing appointment operands.

The combination of these methods (addressing) provides 21 addressing mode.

In this and in the tables below, the following symbols are used:

Direct addressing.

In this case of the addressing method, the location of the byte or data bit is determined by the 8-bit address of the second (and third) Baja command.

Direct addressing is used only to access the internal data memory (Lower 128 bytes of RAM) and special functions registers.

Register addressing.

This addressing method provides access to data that is stored in one of the eight registers R0.

R7 current bank of work registers.

It can also be used to appeal to registers A, B, AB (dual register), register-pointer DPTR and transfer flag.

The address of the specified registers is laid into the operation code, which reduces the number of the command byte.

Indirectly register addressing.

In this case, the address of the data is kept in the index register, the location of which is determined by the operation code.

This addressing method is used to appeal to external RAM and the upper half of the internal RAM.

Registers of 8-bit ad-refers can serve as registers R0, R1 of the selected bank of working registers or SR stack pointer, for 16-bit addressing, only the DPTR Data Delay register is used.

Direct addressing.

With this addressing method, the data is directly indicated in the command and are in the second (or in the second and third) command bytes, i.e.

Not required addressing to memory.

For example, by co-manda MOV A, # 50 in the battery A is loaded number 50.

Index addressing.

This method is an indirectly regime addressing, in which the data byte address is defined as the sum of the contents of the basic (DPTR or PC) and index (s) registers.

Method is-use only to access the program memory and only in read mode;it simplifies viewing tables sewn in memory.

Team structure.

The length of the command is one (49 commands), two (45 ko-mand) or three (17 commands) byte.

The first byte of the command always contains the operability code (KO), A second and third bytes - the addresses of the operands or direct data values.

Separate bits, tetrads, bytes and double-byte words can be used as operands.

You can select 13 types of commands, which are shown in Table. 7.3.5:

● A, PC, SP, DPTR, RN (n \u003d 0, 7) - battery, command meter, stack pointer, data pointer register and current bank register;

● Rm (m \u003d 0, 1) - the register of the current bank used by indirect adrelation;

● Direct - 8-bit address directly addressed operand;

● Bit - address directly addressed bit;

● REL - the relative address of the transition;

● AddR11, ADDR16 - 11- and 16-bit absolute transition address;

● # Data8, # Data16 - direct data (operands) of 8- and 16-bit length;

● A10, A9, A0 - separate discharges of the 11-bit address;

● (.) - The contents of the memory cell at the address specified in brackets;

● Sat, MB - senior and younger bytes of the 16-bit operand.

General Information System.

The command system provides great data processing options in the form of bits, tetrad, bytes, two-byte words, and also real-time control.

To describe the commands, the ASM51 macroassampler language is used. The syntax of most commands consists of a mnemonic designation (abbreviation) of the operation performed, followed by operands.

Using the operands, various ways of addressing and data types are indicated.

In particular, the Abbrevi-Atura MOV has 18 different commands intended for processing three types of data (bits, bytes, addresses) in various address spaces.

The set of commands has 42 mnemonic notation of 111 types of command types for a procure of 33 of the MK functions.

From 111 commands 64 are performed in one machine cycle, 45 - for two cycles and only two commands (MUL - multiplication and div - division) you are fulfilled in 4 cycles. At a clock generator frequency of 12 MHz, the duration of the machine cycle (12 clocks) is 1 μs. By functional signcommands can be divided into five groups. Below is a description of the commands of each group represented in the form of tables. For compactness of the tables, select the team group (Table 7.3.6), the execution of which influences(marked with +) on the state of flagspSW state status register.

Data transfer commands

Sending commands can be divided into individual subgroups.

Shipping commands and data exchange between cells in-memory cells (Table 7.3.7).

Commands 1-16, having mnemonics MOV Dest, SRC, are intended for shipmentbyte or two bytes (command 16) of data from the SRC source to the DEST receiver, while:

● To indicate source(SRC) Four addressing methods are used: Regist-ry (commands 2-4, 6, 8), direct (commands 1, 7, 9, 11), indirect (commands 5, 10) and direct (commands 12-16);

● To indicate receiver(DEST)

three methods are used: register (teams 1, 3 ... 5, 9, 12, 14, 16), straight (teams 2, 7, 8, 10, 13), indirect (commands 6, 11, 15).

Teams 17-20 provide exchangeinformation between the two cells of the internal data memory (or two-sided shipment).

When executing KO-MAND CHCN, the exchange of bytes takes place, and the XCHD command is the younger tetrad byte operands.

One of the cells is always a battery A. As another cell, when exchanging bytes, one of the RN registers of the current bank is used, and also directly or indirectly addressed the internal memory cell; When using notebooks - only indirectly addressable cell of the internal memory.

Since in all MK stack is placed in the inner RAM, in the same subgroup included teams(20, 21) appeals to the stackPUSH SRC, POP DEST.

These commands use only the direct method of addressing, recording bytes on the stack or reinforcing it from the stack.

It should be borne in mind that in those MK, which in the RAM there is no upper 128 bytes, an increase in the stack outside the 128 bytes leads to data loss.

Data transfer commands between internal and external pales (Table 7.3.8).

These commands use only indirect adrelation, while a single-byte address can be located in P0 or R1 of the current bank of the registers, A double-byte address in the DRTR data index register.

With any access to the external memory, the role of the receiver or source of operands in the internal memory is played by the battery A.  Data transfer commands from program memory (Table 7.3.9).

Data transfer commands from program memory (Table 7.3.9).

These commands are designed to read tables from software memory.

MOVC A, @ A + DPTR command is used to appeal to the table with the number of inputs from 0 to 255.

The number of the required login in the table is loaded into the battery, and the DPTR register is installed on the table start point. A distinctive feature of another command is that as a base pointer, a pro-gram counter PC meter is used and accessing the table is made from the subroutine. Initially, the number of the required entry point is loaded into the battery, then the subroutine with the MOVC A, @ A + PC command is called. The table may have 255 EMPs with numbers from 1 to 255, as 0 is used to address the RET command from the subroutine.  Arithmetic data processing commands. All arithmetic commands are performed over unsaluable integers. Operations over two operands (Table 7.3.10). In operations speatAdd additions subject to transferADDC I. subtraction taking into account the loanSubb:

Arithmetic data processing commands. All arithmetic commands are performed over unsaluable integers. Operations over two operands (Table 7.3.10). In operations speatAdd additions subject to transferADDC I. subtraction taking into account the loanSubb:

● The source of one 8-bit operand and the result receiver serves ak-cumulator;

● The source of another operand is either one of the RN (n \u003d 0-7) banking registers, or directly direct.

or indirectly @rm (m \u003d 0, 1) addressed to RAM memory cell, or direct data #Data.

Operations multiplicationMul I. divisionThe div is performed on the contents of the reg recorder A and V. When multiplying, the older 8 results are recorded in a re-gystr in, the youngest 8 discharges - in Register A.

If the product is greater than 255, the OV overflow flag is set; The transfer flag with is always reset. The DIV command performs the division of the 8-bit battery operand A on the 8-bit operand of Register V.

When dividing private (older discharges) is recorded in a re-gystr in a, the residue (younger discharges) - in B. Flags of transferring C and OV overflows are reset.

When you try to divide 0, the OV overflow flag is set. The division operation is more often used for shifts and transformations of numbers.

When dividing a binary number by 2 N, it shifts on n bits to the left.

Extra bits are transferred to Register V.

Single Operands Operations(Table. 7.3.11).

The DA command is used to perform binary-decimal operations. Inc commands, DEC allow you to increase or decrease the contents of the memory cell on one.

They are applicable to the contents of the battery-RA A, one of the RN working registers or memory cells addressable both directly and indirectly.

An increase operation per unit also applies to the contents of a 16-bit DPTR pointer register.

Commands of logical operations.

Dual operations

(Table 7.3.12).

Commands AML, ORL, XRL allow you to perform three two-dimensional logic operations over 8-bit operands: anL - logical multiplication (and), ORL - Lo-hyphenation (OR), XRL - excluding or (xor).

Operations are performed above individual bits of operands. The source of one of the operands and simultaneously the result receiver is either a battery (a), or directly addressing the memory cell (Direct).

For the source of another operand, a regi-string, direct, indirect or direct addressing method is used.

Single operations

(Table 7.3.13).

The group includes a number of single operations over the contents of the battery A: cleaning operations (CLR), logical addition or inversion (CPL), cyclic and extended cyclic shifts to 1 bit to the right (RL, RLC) and Left (RR, RRC), exchange Tetrad or cyclic byte shift by 4 discharge (SWAP), and an empty operation (NOP), as a result of which the state of all MK registers (with the exception of a program counter) remains unchanged.

Management commands

Unconditional transition teams

(Table 7.3.14).

Commands 1-3 differ only on the format of the destination address.

The LJMP co-mand (L - LONG) performs a "long" unconditional transition to the specified address of the AddR16, uploading the PC counter with the second and third command bytes.

The command provides a transition to any point of 64k byte address space.

Co-manda AJMP (A - Absolute) provides an "absolute" transition to the address inside the 2K byte page, the initial address of which is specified by five older discharge-ds of the PC program meter (first the contents of PC increase by 2).

The SJMP (S - Short) command allows you to implement a "short" unconditional transition to the address that is calculated by the addition of the REL offset with a sign in the second pate commands with the contents of the PC counter, previously enlarged by 2.

The transition address is within -128 + 127 bytes relative to the adreth team.

To move to any other point of 64-kilobyte address pro-space, a command 4 can also be used with an indirect @ A + DPTR adrelation.

In this case, the contents A is interpreted as a whole sign.  An empty operation (NOP), as a result of which the state of all the registers of the microprocessor (with the exception of the program meter) remains unchanged.

An empty operation (NOP), as a result of which the state of all the registers of the microprocessor (with the exception of the program meter) remains unchanged.

Conditional transition teams

(Table 7.3.15).

Using the JZ and JNZ commands, the transition is performed if the battery content is respectively or not zero.

The transition address is calculated by addition of the relative iconic displacement of the REL with the contents of the PC command counter after adding to it number 2 (the command lengths in bytes).

The contents of the battery remains non-modified.

Teams on flags do not affect.  CJNE (3-6) commands are used to implement a conditional transition based on the result of a comparison of two 8-bit operands, the location of which is indicated in the command.

CJNE (3-6) commands are used to implement a conditional transition based on the result of a comparison of two 8-bit operands, the location of which is indicated in the command.

If their values \u200b\u200bare not equal, the transition is carried out.

The transition address is calculated by the addition of the REL offset with the contents of the PC counter, pre-tightened by 3.

Otherwise, the following command is performed.

The graph of the algorithm shows the effect of the values \u200b\u200bof the compared 8-bit operands on the transfer flag of C.

DJNZ (7, designed to organize software cycles.

The RN register or directly (Direct) addressable cell is a second-time cycle counter, a REL (in the second and third command bytes) is the relative address of the transition to the beginning of the cycle.

When executing commands, the contents of the meter decreases per unit and is checked to zero.

If the content count is not zero, the transition to the beginning of the cycle is carried out.

In a person, the next team is performed.

The transition address is calculated by the addition of offset with the contents of the counter, previously increased for the co-mandy length (by 2 or 3).

The command flags do not affect.

Call commands to subroutines and return from programs

(Table 7.3.16).

LCALL commands "Long Call" and ACALL "Absolute Call" carry out an unconditional call of the subroutine posted at the specified address.

The difference between these commands from the unconditional transition commands discussed above is that they retain the return address (counter content) to the main program.

The return command from the RET subroutine restores the contents of the command meter from the stack, and the RETI command besides this permissions of the maintenance level.  The control commands are widely used by relative addresses, which supports moving software modules.

The control commands are widely used by relative addresses, which supports moving software modules.

As a relative address, an 8-bit REL displacement with a sign is provided, providing a branching from the current position of the PC counter in both directions by ± 127 bytes.

To go to any other point of 64k-byte address space, either the direct address of the AddR16 can be used, or an indirect @ A + DPTR address.

In the latter case, the contents are interpreted as a whole without a sign.

Var-AnT by the short direct addressing of the AddR11 inside the 2k-byte current page of Wen-den for compatibility with the MK48 architecture.

All of these addressing types can be applied only to the transition operation, a for the call operation is permissible only direct addr16 and internal addr11 addressing methods.

In all conditional operations, only relative addressing can be used.

When MK51 identifies the interrupt request, it generates one of the LCALL AddR16 type commands, which automatically ensures that the address of the return address in the stack.

However, unlike MK48 in MK51, there is no automatically saved in-formation on the status.

In this case, the logic of interrupts ceases to work on requests of the level that was accepted for maintenance.

To reduce the interrupt level, the return command from the Reti interrupt is served, which, in addition to the opera, equivalent to RET, includes an interrupt permission operation of this level.

Typical conditional operations of MK51 also include JZ, JNZ operations.

ON-NAO appeared a new operation "Compare and Go" CJNE.

According to this command, the operand is first compared by the rules for subtracting integers with the constant and in accordance with the result of the comparison, the CY flag is then displayed. Then, in case of incomprehension with the constant, branching is performed. Comparing the battery, re-gastro or memory cell with a consistency of the constant, we obtain a convenient way to check for coincidences, for example, in order to identify special occasions.

In fact, the CJNE command is an element of the operator of the high-level CASE type.

Further development received the DJNZ team.

Now a programmer can use not only one of the RN working registers, but also a dseg memory cell.

Bit operations commands.

The group consists of 12 commands that allow you to complete operations on one or two bits (reset, installation, bit inversion, and logical and or or or), and 5 commands designed to implement conditional transitions (Table 7.3.17).

Commands provide a direct addressing of 128 bits located in the six-tissure cells of the internal RAM with addresses 20h.

2fh (Table 7.3.3), and 128 bits located in special purpose registers, the addresses of which are multiple eight (highlighted in Table 7.3.4 by bodies).

When performing operants over two single-digit operands as a logical accumulator, the PSW register trigger storing the transfer flag c (Table 7.1.2) is used.

MOV commands (1,2) are carried out shippingbit from one directly addressable bit cell of the internal RAM into trigger C or in the opposite direction.

CRL (3, 4), SETB (5, 6), SETB (5, 6), respectively resetto zero or set-vita unit of transfer flag C or specified bit.

With the help of CPL, ANL, ORL (7-12) commands, logical operations of inversion, addition and multiplication are performed.

The group also includes teams (13-17) to implement conventional transition operations with relative 8-bit REL displacement.

Transitions can be implemented both with a mounted bit or flag of the transfer (commands 13, 16) and at the discharge (command 14, 17).

The JBC command in addition to the transition to the calculating address when executing the condition (BIT) \u003d 1, reset this bit into the zero state.

When performing conditional transition commands, the address transition is calculated after adding the contents of the number 3 or 2 counter (reflecting the number of bytes in the command).

- Arithmetic teams;

- Logical commands;

- Data transfer commands;

- Bite processor commands;

- Commands branch and management.

- Register addressing

- Direct addressing

- Indirectly register addressing

- Direct addressing

- Indirect register addressing on the amount of basic and index registers

| Designation, symbol | Purpose |

| BUT | Battery |

| RN. | Registers of the current selected register bank |

| R. | The number of the downloaded register, specified in the team |

| Direct. | Directly addressable 8-bit internal address of a data cell, which can be the cell of the internal data RAM (0-127) or SFR (128-255) |

| @Rr. | Indirectly addressable 8-bit cell of the internal data RAM |

| Data8. | 8-bit direct me, walking in a cop |

| Datah | Senior bits (15-8) of immediate 16-bit data |

| Datal | Younger bits (7-0) of immediate 16-bit data |

| ADDR11 | 11-bit destination address |

| ADDRL | Junior destination addresses |

| DISP8. | 8-bit offset byte with m sign |

| Bit. | Bit with direct addressing, the address of which contains a cop being in the internal data RAM or SFR |

| A15, A14 ... A0 | Destination addresses bits |

| (X) | The contents of the element x. |

| ((X)) | Contents at the address stored in the X Element |

| (X) [M] | Discharge m element x |

| + - * / and or xor / x | Operations: addition to subtracting the multiplication of the division of logical multiplication (operation and) of logical addition (operation or) addition of module 2 (excluding or) inversion of element x |

Mnemonic designations of functions are uniquely related to specific combinations of addressing methods and data types. In total, 111 such combinations are possible in the command system. The table shows the list of commands ordered by alphabetically.

| Mnemonics | Function | Flags |

| ACALL command | Absolute call of the subroutine | |

| Team Add A,<байт-источник> | Addition | AC, C, OV |

| ADDC A team<байт-источник> | Addition with transfer | AC, C, OV |

| AJMP command | Absolute transition | |

| AnL team<байт-назначения>, <байт-источникa> | Logical "and" | |

| ANL C command,<байт-источникa> | Logical "and" for variables-bits | |

| CJNE command<байт-назначения>, <байт-источник>, <смещение> | Comparison and transition, if not equal | C. |

| Team CLR A. | Battery reset | |

| CLR Team | Bit reset | C, Bit. |

| CPL A. Team | Inversion AK Uma Ura | |

| CPL command | Bit Inversion | C, Bit. |

| Team Da A. | Decimal Battery Correction for False | AC, C. |

| Team dec<байт> | Decrement | |

| Div AB Team | Division | C, OV. |

| Team djnz.<байт>, <смещение> | Decrement and transition, if not zero | |

| Inc. command<байт> | Increment | |

| Team Inc DPTR | Increment of data pointer | |

| JB Team | Transition if the bit is installed | |

| Team jbc. | Transition if the bit is installed and reset this bit | |

| JC Team | Transition if the transfer is set | |

| JMP @ A + DPTR team | Indirect transition | |

| Team jnb. | Transition if the bit is not installed | |

| JNC team | Transition if the transfer is not installed | |

| Team jnz. | Transition if the battery content is not zero | |

| Team jz. | Transition if the contents of the battery are 0 | |

| LCALL command | Long challenge | |

| Team ljmp | Long transition | |

| Team MOV.<байт-назначения>, <байт-источника> | Send a variable byte | |

| Team MOV.<бит-назначения>, <бит-источника> | Send data bits | C. |

| Team MOV DPTR, # Data16 | Upload data pointer 16-bit constant | |

| MOVC A, @ A + ( | Send bytes from program memory | |

| MOVX command<байт приемника>, <байт источника> | Send to external memory (from external memory) data | |

| Team Mul AB. | Multiplication | C, OV. |

| Command NOP. | No operation | PC. |

| ORL team<байт-назначения>, <байт-источникa> | Logical "or" for variable bytes | |

| ORL C command<бит источникa> | Logical "or" for variables-bits | C. |

| Pop Team | Reading from stack | |

| Push team | Record in stack | |

| RET. | Return from subroutine | |

| Reti team | Return from interrupt | |

| RL A. Team | Battery Content Shift Left | |

| RLC A command | Battery Content Shift Left Via Transpiration Flag | |

| RR A command | Battery shift to the right | |

| RRC A command | Battery content shift to the right through the transfer flag | C. |

| SETB command | Set bits | C. |

| Team SJMP.<метка> | Short transition | |

| SUBB A,<байт источника> | Subtraction with borrowing | AC, C, OV |

| SWAP A. | Exchange of notebooks inside the battery | |

| XCH A team<байт> | Battery Battery Content Sharing | |

| Team Xchd A, @ R1 | Tetraja exchange | |

| XRL team<байт-назначения>, <байт-источникa> | Logical "excluding or" for variable bytes |

Plan lectures

1. Introduction

2. Arithmetic and logical instructions

3. Data transfer commands

4. Boolean operations

5. Translation instructions

1. Introduction

Team system MCS-51. Supports a single set of instructions, which is designed to perform 8-bit executive device management algorithms. There is the possibility of using rapid addressing methods for internal RAM, the implementation of bit operations over small data structures. There is a detailed system for addressing single-bit variables as an independent data type that allows you to use individual bits in logical and control commands of the Boolean algebra.

Addressing modes : Set of commands MCS-51. Supports the following addressing modes. Direct addressing: Operand is defined by an 8-bit address in the instructions. Direct addressing is used only for the younger half of the internal memory of the data and registers. Sfr.. Indirect addressing: The instruction addresses the register containing the operand address. This type of addressing is used for external and internal RAM. Registers can be used to specify 8-bit addresses R0 and R1 selected register bank or stack pointer Sp.. For the 16-bit addressing, only the data pointer register is used. DPTR..

Register instructions : Registers R0-R7 The current register bank can be addressed through specific instructions containing a 3-bit field indicating the register number in the instructions itself. In this case, the corresponding address field is missing. Operations using special registers: Some instructions use individual registers (for example, battery operations, DPTR., etc.). In this case, the operand address is generally not specified in the command. It is predetermined by the operation code.

Direct Constants : The constant can be directly in the command when the operation code.

Index addressing : Index addressing can only be used to access the program memory and only in read mode. In this mode, the tables are viewed in the program memory. 16-bit register ( DPTR. Or the program counter) indicates the basic address of the required table, and the battery indicates the entry point in it.

Set of commands It has 42 mnemonic symbols for specifying 33 functions of this system. The syntax of most assembly language commands consists of a mnemonic designation of the function, followed by operands indicating the addressing methods and data types. Various data types or addressing modes are determined by the installed operands, and not changes in mnemonic designations.

The command system can be conventionally located for five groups: arithmetic commands; logical commands; data transfer commands; bite processor commands; Commands branch and management. Designations and symbols used in the command system are given below.

Table. Designations and Symbols used in the command system

|

Designation, symbol |

Purpose |

|

Battery |

|

|

Registers of the current selected register bank |

|

|

The number of the loaded register specified in the command |

|

|

direct. |

Directly addressable 8-bit internal address of the data cell, which can be the cell of the internal data RAM (0-127) or the SFR special functions register (128-255) |

|

Indirectly addressable 8-bit cell of the internal data RAM |

|

|

8-bit direct This, which is included in the operation code (CPA) |

|

|

datah |

Senior bits (15-8) of immediate 16-bit data |

|

datal |

Younger bits (7-0) of immediate 16-bit data |

|

11-bit destination address |

|

|

aDDRL |

Junior destination addresses |

|

8-bit shift byte with sign |

|

|

Bit with direct addressing, the address of which contains a cop in the internal data RAM or the SFR special functions register |

|

|

a15, A14 ... A0 |

Destination addresses bits |

|

The contents of the element x. |

|

|

Contents at the address stored in the X Element |

|

|

Discharge m element x |

|

|

|

Operations: |

Mnemonic designations of functions are uniquely related to specific combinations of addressing methods and data types. In total, 111 such combinations are possible in the command system.

2. Arithmetic and logical instructions

Like P. riemer arithmetic teamThe addition operation can be executed by one of the following commands.

Add.A.,7 F. 16 - add to the content of the registers and number 7F 16. and the result is maintained in the register A;

Add.A.,@ R.0 - add to the content of the register and the number whose address (@ – commercial aT. ) Stored in the RegisterR. 0 (indirect addressing), and the result is maintained in the register A;

Add a, R7 - add to the content of the register and the contents of the registerR. 7 and the result is maintained in the register A;

Add a, # 127 - add to the content of the register and the number, the address of the storage cell of which 127 ( # - number symbol), and the result is saved to regis t.- RE A.

All arithmetic instructions are performed in one machine cycle except for the command. Inc DPTR. (data pointer shift DPTR. The next byte) requiring two machine cycles, as well as multiplication and division operations performed for 4 machine cycles. Any byte in the internal data memory may be incremented and decremented without using the battery.

Instruction Mul AB Multiplication (multiplication - multiplication) of data in the battery on the data in the register b, placing a product in registers A (younger half) and B (older half).

Instruction Div AB Division (Division - division) The contents of the battery to the value in the register B leaving the residue in b, and the private is in the battery.

Instruction Da A. Designed for binary-decimal arithmetic operations (arithmetic operations on the numbers presented in binary-decimal code). She does not transform binary numbers in binary-decimalbut only provides the correct result when adding two binary-decimal numbers.

Example logical team: Operation of logical and can be performed by one of the following commands:

AnlA.,7 F. 16 - logical multiplication of the content of the register and number 7F 16. and the result is preserved in the register A;

AnlA.,@ R.1 - logical multiplication of the content of the register and the number, the address of which is stored in the registerR. 1 (indirect addressing), and the result is maintained in the register A;

Anl A, R6 - logical multiplication of the contents of the register A on the contents of the registerR. 6, and the result is maintained in the register A;

Anl a, # 53 - logical multiplication of the contents of the register and the number, the address of the storage cell of which 53 16, and the result is maintained in the register A.

All logic operations on the contents of the battery are performed in one machine cycle, the rest - for two. Logical operations can be made above any of the lower 128 bytes of the internal data memory or over any register. Sfr. (Special functions registers) in direct addressing mode without using battery.

Operations of the cyclic shift RL A, RLC a, etc. Move the contents of the battery to one bit to the right or left. In the case of the left cyclic shift, the younger bit moves to the older position. In the case of the right cyclic shift, the opposite occurs.

Operation SWAP A. Exercise the exchange of younger and senior tetrad in the battery.

3. Data transfer commands

Team MOV Dest, SRC Allows you to send data between the cells of the internal RAM or the register area of \u200b\u200bspecial functions Sfr. Without using battery. At the same time, work with the upper half of the internal RAM can be carried out only in the mode of indirect addressing, and the appeal to registers Sfr. - Only in direct addressing mode.

In all microcircuits MCS-51. The stack is located directly in the data residency and increases upwards. Instruction Push. Initially increases the value in the stack pointer register Sp.and then writes to the data byte stack. Teams Push. and Pop Used only in direct addressing mode (recording or restoring bytes), but the stack is always available at indirect addressing through the register Sp.. Thus, the stack can also use the upper 128 data byte of the data. These considerations eliminate the possibility of using stall commands to address registers Sfr..

Data Instructions include a 16-bit shipment operation. Mov DPTR, # Data16used to initialize the data pointer register DPTR. When viewing tables in software memory or access to the external data memory.

Operation XCH A, BYTE It is used to exchange data between the battery and the addressable byte. Team Xchd A, @ Ri Similar to the previous one, but is performed only for junior tetrad involved in the exchange of operands.

To access the external data memory, only indirect addressing is used. In the case of single-byte addresses, registers are used R0 or R1 current register bank, and for 16-bit - data pointer register DPTR.. With any access to the external data memory, the battery plays the role of the source or receiver information.

To access tables posted in software memory, commands are used:

MOVC A, @ A + DPTR ;

MOVC A, @ A + PC. .

As the base address of the table uses the contents of the data indicator register DPTR. or PC. (program meter), and the offset is taken from A.. These commands are used exclusively to read data from the program memory, but not to write to it.

4. Boolean operations

Microcircuits MCS-51. Contain in its composition "Boolean" processor. The internal RAM has 128 directly addressed bits. Space register registers Sfr. May also support up to 128 bite fields. Bit instructions carry out conditional transitions, shipments, reset, inversions, operations "and" or "or". All specified bits are available in direct addressing mode.

Transfer bit CF. In the register of special functions "The word status of the program PSW."Used as a single battery of a Boolean processor.

5. Translation instructions

Addresses of transition operations are indicated in the assembler language with a label or a real value in the program memory space. Conditional transition addresses are assembled into a relative displacement - a sign byte added to the program meter PC. In the case of the transition condition. The boundaries of such transitions lie within between minus 128 and 127 relative to the first byte following the instructions. In the register of special functions "The word status of the program PSW.»There is no zero flag, so instructions JZ. and Jnz. Check the condition "equal to zero" as testing data in the battery.

There are three types of team of unconditional transition: SJMP, Ljmp and AJMP - Distinguished destination address format. Instruction SJMP Codes the address as a relative displacement, and takes two bytes. The range of transition is limited by the range from minus 128 to 127 bytes relative to the instruction following SJMP.

In the instructions Ljmp Use the destination address in the form of a 16-bit constant. The length of the command is three bytes. The destination address can be located anywhere in the program memory.

Team AJMP uses a 11-bit address constant. The command consists of two bytes. When this manual is executed, the younger 11 bits of the address counter are replaced by a 11-bit address from the command. Five senior program counter bits PC. remain unchanged. Thus, the transition can be made inside the 2k-byte block in which the instruction is located following the command AJMP.

There are two types of command calls of the subroutine: Lcall and Acall. Instruction Lcall Uses the 16-bit address of the called subroutine. In this case, the subroutine can be located anywhere in the memory of the programs. Instruction Acall Uses the 11-bit address of the subroutine. In this case, the called subroutine must be located in one 2K-byte block with the instruction following Acall. Both variants of the command lay the next command address and download to the software counter. PC. corresponding new meaning.

The subprogram is completed by the instruction RET.allowing you to return to the instruction next command Call. This instruction removes the return address from the stack and loads it into the program counter. PC. . Instruction Reti. Used to return from interrupt processing routines. The only difference Reti. from RET. is that Reti. Informs the system that the interrupt processing has ended. If at the time of execution Reti. no other interrupts, then it is identical RET..

Instruction Djnz. Designed to control cycles. To execute cycles N. Once it is necessary to download in the byte counter with the value N. and close the body cycle team Djnz.pointing to the beginning of the cycle.

Team CJNE. Compares the two of its operand as unsigned integers and transitions to the address specified in it if the compaable operands are not equal. If the first operand is less than the second, then the transfer bit CF. Installed in "1".

All commands in the assembled form occupy 1, 2 or 3 bytes.

Architecture microcontrollers

Understanding the microcontroller architecture is key when learning the assembler type programming languages. Assembler structure, format of its commands, addressing operands, etc. Fully determined by architecture. The purpose of studying architecture is:

· Detection of sets available for programming registers, functional purposes and structure;

· Understanding the organization of RAM and the procedure for its use;

· Acquaintance with data types;

· Study of the format of machine commands;

· Finding out the organization of the processing of interrupts.

The architecture of the MCS-51 family is largely predetermined by its purpose - building compact and cheap digital devices. All MK functions are implemented using a single chip. The MCS-51 family includes a number of microcircuits from the simplest microcontrollers to quite complicated. MCS-51 family microcontrollers allow you to perform both control tasks of various devices and implement individual analog circuit nodes. All chips of this family work with the same command system, most of them are performed in the same enclosures with the coinciding basement (the numbering of the terminals for the case). This allows you to use for the developed microcircuit devices of different manufacturers (such asintel, dallas, atmel, philips, etc.) without alteration of the concept of the device and the program.

MCS-51 is made by Harvard architecture, where the address spaces of the memory and data are separated.

The block diagram of the controller is presented in Fig. 2.3 and consists of the following main functional nodes: a control unit, an arithmetic logical device, a block of timer / counters, serial interface and interrupts, software meter (command meter), data memory and program memory.

Bilateral exchange is carried out using an internal 8-bit data line. Consider a Read more assigning each block. According to such a scheme, almost all representatives of the MCS-51 family are built. The various chips of this family differ only in special purpose registers (including the number of ports). The system of commands of all the controllers of the MCS-51 family contains 111 basic commands with a format 1, 2 or 3 bytes and does not change during the transition from one chip to the other. It provides excellent portability of programs from one chip to another.

Control and synchronization unit (Timing and Control) is designed to generate synchronizing and control signals that ensure the coordination of joint work of the OEEHM blocks in all permissible modes of its operation. The control unit includes:

- temporary interval formation device,

- i / O combination circuit

- team register,

- decifranger teams.

Entrance and weekend signals of the control and synchronization block:

1 PSEN. - resolution of software memory;

2 Ale. - the output signal of the permission of the address fixation;

3 Prog - programming signal;

4 EA. - blocking work with internal memory;

5 VPP. - programming voltage;

6 RST - Common reset signal.

The time interval generation device is necessary to synchronize the sequence of the states of the CPU forming the machine cycle, as well as for the proper operation of all internal detectors and output buffers of ports. The machine cycle consists of six sequences (states) from S1 to S6, each of which, in turn, is divided into two phases:

phase 1 (Phase 1 - P1) and phase 2 (Phase 2 - P2). Thus, the machine cycle can be defined as a sequence of time intervals S1P1, S1P2, S2P1, ...., S6P2. The duration of the phase is equal to the period of the clock pulse, so the machine cycle takes 12 clock periods.

The number of machine cycles determines the time of execution of commands. Almost all commands are performed for one or two machine cycles, except for multiplication and division commands, the duration of which is four engine cycles. I / O logic is intended for receiving and issuing signals that provide the exchange of information with external devices through the output ports of the P0-P3 output.

Register of teams Designed for recording and storing 8-bit code executable code. The operation code, using the command decoder and the computer control logic, is converted into the microprogram of the execution of the command.

Figure 2.3. Structural diagram of an Intel 8051 microcontroller

(MCS-51 family)

Arithmetic logical device (ALU) is a parallel eight-bit device that ensures the execution of arithmetic and logical operations. Alu consists of:

- temporary storage registers -TMP1 and TMP2,

- ROM constant,

- adder

- additional register - register in,

- battery - ACC,

- register status register (Flag register) - PSW.

Temporary Storage Registers TMP1, TMP2 - Eight-bit registers intended for receiving and storing operands at the time of operations on them. These registers are not programmatically accessible.

ROM Constant Provides a corrective code to generate a binary-decimal data view, a mask code for bit operations and a constant code.

Parallel eight-bit adder It is a scheme of a combination type with a sequential transfer, intended for performing arithmetic operations of addition, subtraction and logical operations of addition, multiplication, unequivocalities and identity.

Register B. - The eight-bit register used during multiplication and division operations. For other instructions, it can be viewed as an additional ultraoperative register.

Battery- Eight-bit register designed to receive and storing the result obtained when performing arithmetic and logical operations or shift operations.

PSW Program Status Register (Program Status Word)designed to store the status of the commands performed. When performing many teams in ALU, a number of features of operation (flags) are formed, which are recorded in the program status register (PSW). In tab. 1 shows a list of PSW flags, their symbolic names are given and the conditions for their formation are described.

Interrupt and Serial Interface Block - UART (Universal Asynchronous Receiver / Transmitter) Designed to organize an input - withdrawal of consistent information flows and organization of the program interrupt system.By definition, the interrupt means the temporary termination of the main process of computing to perform some planned or unplanned actions caused by the work of equipment or programs.

These actions can wear a service character, be requests from the user program to perform the service or be a reaction to abnormal situations.

Cellular - what it is on the iPad and what's the difference

Cellular - what it is on the iPad and what's the difference Go to digital television: What to do and how to prepare?

Go to digital television: What to do and how to prepare? Social polls work on the Internet

Social polls work on the Internet Savin recorded a video message to the Tyuments

Savin recorded a video message to the Tyuments Menu of Soviet tables What was the name of Thursday in Soviet canteens

Menu of Soviet tables What was the name of Thursday in Soviet canteens How to make in the "Word" list alphabetically: useful tips

How to make in the "Word" list alphabetically: useful tips How to see classmates who retired from friends?

How to see classmates who retired from friends?