Процессоры. Перемещение контроллера памяти непосредственно в современные процессоры Что такое интегрированное встроенный контроллер памяти

Кажется, что Intel в этом отношении догоняет AMD. Но, как часто бывает, когда гигант что-то делает, то и шаг вперёд получается гигантским. Если у Barcelona используется два 64-битных контроллера памяти DDR2, топовая конфигурация Intel включает целых три контроллера памяти DDR3. Если установить память DDR3-1333, которую Nehalem тоже будет поддерживать, это даст пропускную способность до 32 Гбайт/с в некоторых конфигурациях. Но преимущество встроенного контроллера памяти кроется не только в пропускной способности. Он существенно снижает задержки доступа к памяти, что не менее важно, учитывая, что каждый доступ стоит несколько сотен тактов. В контексте настольного использования снижение задержек встроенного контроллера памяти можно приветствовать, однако полное преимущество от более масштабируемой архитектуры будет заметно в многосокетных серверных конфигурациях. Раньше при добавлении CPU доступная пропускная способность оставалась прежней, однако теперь каждый новый дополнительный процессор увеличивает пропускную способность, поскольку каждый CPU обладает собственной памятью.

Конечно, чудес ожидать не следует. Перед нами конфигурация Non Uniform Memory Access (NUMA), то есть доступ к памяти будет обходиться по тем или иным накладным расценкам, в зависимости от того, где данные располагаются в памяти. Понятно, что доступ к локальной памяти будет производиться с самыми низкими задержками и самой высокой пропускной способностью, поскольку доступ к удалённой памяти происходит через промежуточный интерфейс QPI, снижающий производительность.

|

Нажмите на картинку для увеличения.

Влияние на производительность предсказать сложно, поскольку всё зависит от приложения и операционной системы. Intel утверждает, что падение производительности при удалённом доступе по задержкам составляет около 70%, а пропускная способность снижается в два раза по сравнению с локальным доступом. По информации Intel, даже при удалённом доступе через интерфейс QPI, задержки будут ниже, чем на предыдущих поколениях процессоров, где контроллер находился на северном мосту. Однако это касается только серверных приложений, которые уже довольно долгое время разрабатываются с учётом конфигураций NUMA.

Иерархия памяти в Conroe была очень простой; Intel сконцентрировалась на производительности общего кэша L2, который стал лучшим решением для архитектуры, которая нацеливалась, главным образом, на двуядерные конфигурации. Но в случае с Nehalem инженеры начали с нуля и пришли к такому же заключению, что и конкуренты: общий кэш L2 не очень хорошо подходит для "родной" четырёхъядерной архитектуры. Разные ядра могут слишком часто "вымывать" данные, необходимые другим ядрам, что приведёт к слишком многим проблемам с внутренними шинами и арбитражем, пытаясь обеспечить все четыре ядра достаточной пропускной способностью с сохранением задержек на достаточно низком уровне. Чтобы решить эти проблемы, инженеры оснастили каждое ядро собственным кэшем L2. Поскольку он выделен на каждое ядро и относительно мал (256 кбайт), получилось обеспечить кэш очень высокой производительностью; в частности, задержки существенно улучшились по сравнению с Penryn - с 15 тактов до, примерно, 10 тактов.

Затем есть огромная кэш-память третьего уровня (8 Мбайт), отвечающая за связь между ядрами. На первый взгляд архитектура кэша Nehalem напоминает Barcelona, но работа кэша третьего уровня очень отличается от AMD - она инклюзивная для всех нижних уровней иерархии кэша. Это означает, что если ядро попытается получить доступ к данным, и они отсутствуют в кэше L3, то нет необходимости искать данные в собственных кэшах других ядер - там их нет. Напротив, если данные присутствуют, четыре бита, связанные с каждой строчкой кэш-памяти (один бит на ядро) показывают, могут ли данные потенциально присутствовать (потенциально, но без гарантии) в нижнем кэше другого ядра, и если да, то в каком.

Эта техника весьма эффективна для обеспечения когерентности персональных кэшей каждого ядра, поскольку она уменьшает потребность в обмене информацией между ядрами. Есть, конечно, недостаток в виде потери части кэш-памяти на данные, присутствующие в кэшах других уровней. Впрочем, не всё так страшно, поскольку кэши L1 и L2 относительно маленькие по сравнению с кэшем L3 - все данные кэшей L1 и L2 занимают, максимум, 1,25 Мбайт в кэше L3 из доступных 8 Мбайт. Как и в случае Barcelona, кэш третьего уровня работает на других частотах по сравнению с самим чипом. Следовательно, задержка доступа на данном уровне может меняться, но она должна составлять около 40 тактов.

Единственные разочарования в новой иерархии кэша Nehalem связаны с кэшем L1. Пропускная способность кэша инструкций не была увеличена - по-прежнему 16 байт на такт по сравнению с 32 у Barcelona. Это может создать "узкое место" в серверно-ориентированной архитектуре, поскольку 64-битные инструкции крупнее, чем 32-битные, тем более что у Nehalem на один декодер больше, чем у Barcelona, что сильнее нагружает кэш. Что касается кэша данных, его задержка была увеличена до четырёх тактов по сравнению с тремя у Conroe, облегчая работу на высоких тактовых частотах. Но закончим мы на положительной новости: инженеры Intel увеличили число промахов кэша данных L1, которые архитектура может обрабатывать параллельно.

TLB

Уже многие годы процессоры работают не с физическими адресами памяти, а с виртуальными. Среди других преимуществ такой подход позволяет выделять программе больше памяти, чем есть в компьютере, сохраняя только необходимые на данный момент данные в физической памяти, а всё остальное - на жёстком диске. Это означает, что каждый доступ к памяти виртуальный адрес нужно переводить в физический адрес, и для сохранения соответствия приходится использовать огромную таблицу. Проблема в том, что эта таблица получается столь большой, что на чипе её хранить уже не получается - она размещается в основной памяти, причём её можно даже сбрасывать на жёсткий диск (часть таблицы может отсутствовать в памяти, будучи сброшенной на HDD).

Если для каждой операции работы с памятью требовался бы такой этап перевода адресов, то всё работало бы слишком медленно. Поэтому инженеры вернулись к принципу физической адресации, добавив небольшую кэш-память напрямую на процессор, которая хранит соответствие для нескольких недавно запрошенных адресов. Кэш-память называется Translation Lookaside Buffer (TLB). Intel полностью переделала TLB в новой архитектуре. До сих пор Core 2 использовал TLB первого уровня очень маленького размера (16 записей), но очень быстрый и только для загрузок, а также больший кэш TLB второго уровня (256 записей), который отвечал за загрузки, отсутствующие в TLB L1, а также и записи.

Nehalem теперь оснастился полноценным двухуровневым TLB: кэш TLB первого уровня разделён для данных и инструкций. Кэш TLB L1 для данных может хранить 64 записи для маленьких страниц (4K) или 32 записи для больших страниц (2M/4M), а кэш TLB L1 для инструкций может хранить 128 записей для маленьких страниц (как и в случае Core2), а также семь для крупных. Второй уровень состоит из унифицированного кэша, который может хранить до 512 записей и работает только с маленькими страницами. Цель такого улучшения заключается в увеличении производительности приложений, которые используют большие массивы данных. Как и в случае двухуровневой системы предсказания ветвлений, перед нами ещё одно свидетельство серверной ориентации архитектуры.

Давайте на время вернёмся к SMT, поскольку эта технология тоже влияет на TLB. Кэш L1 TLB для данных и TLB L2 динамически распределяются между двумя потоками. Напротив, кэш L1 TLB для инструкций статически распределяется для малых страниц, а выделенный для больших страниц полностью копируется - это вполне понятно, учитывая его малый размер (семь записей на поток).

Доступ к памяти и предварительная выборка

Оптимизированный невыровненный доступ к памяти (Unaligned Memory Access)

В архитектуре Core доступ к памяти приводил к ряду ограничений по производительности. Процессор был оптимизирован для доступа к адресам памяти, выровненным по 64-байтным границам, то есть по размеру одной строчки кэша. Для невыровненных данных доступ был не только медленный, но и выполнение невыровненных инструкций считывания или записи было более накладным, чем в случае выровненных инструкций, независимо от реального выравнивания данных памяти. Причина заключалось в том, что эти инструкции приводили к генерации нескольких микроопераций на декодерах, что снижало пропускную способность с данными типами инструкций. В итоге компиляторы избегали генерировать инструкции подобного типа, подставляя вместо них последовательность инструкций, которые менее накладны.

Так, чтение из памяти, при котором происходил перехлёст двух строчек кэша, замедлялось примерно на 12 тактов, по сравнению с 10 тактами для записи. Инженеры Intel оптимизировали подобный тип обращений, чтобы он выполнялся быстрее. Начнём с того, что теперь нет падения производительности при использовании невыровненных инструкций чтения/записи в случаях, когда данные выровнены в памяти. В других случаях Intel тоже оптимизировала доступ, снизив падение производительности по сравнению с архитектурой Core.

Больше блоков предварительной выборки с более эффективной работой

В архитектуре Conroe Intel особенно гордилась аппаратными блоками предсказания. Как вы знаете, блок предсказания - это механизм, который следит за характером доступа к памяти и пытается предсказать, какие данные потребуются через несколько тактов. Цель заключается в том, чтобы упреждающим образом загрузить данные в кэш, где они будут располагаться ближе к процессору, и вместе с тем максимально использовать доступную пропускную способность тогда, когда процессору она не нужна.

Данная технология даёт замечательные результаты с большинством настольных приложений, но в серверной среде она часто приводила к потере производительности. Есть несколько причин подобной неэффективности. Во-первых, доступы к памяти часто сложнее предсказать в серверных приложениях. Доступ к базе данных, например, отнюдь не линейный - если в памяти запрашивается какой-либо элемент данных, то это не значит, что следующим будет соседний элемент. Это ограничивает эффективность блока предварительной выборки. Но основной проблемой была пропускная способность памяти в многосокетных конфигурациях. Как мы уже говорили раньше, она уже была "узким местом" для нескольких процессоров, но, помимо этого, блоки предварительной выборки приводили к дополнительной нагрузке на этом уровне. Если микропроцессор не выполняет доступ к памяти, то включались блоки предварительной выборки, пытаясь использовать пропускную способность, по их предположению, свободную. Однако блоки не могли знать, нужна ли эта пропускная способность другому процессору. Это означало, что блоки предварительной выборки могли "отбирать" у процессора пропускную способность, которая и так была "узким местом" в таких конфигурациях. Чтобы решить эту проблему, Intel не нашла ничего лучше, как отключить блоки предварительной выборки в таких ситуациях - вряд ли самое оптимальное решение.

Как утверждает Intel, эта проблема уже решена, однако компания не даёт никаких деталей по поводу работы новых механизмов предварительной выборки. Всё, что компания говорит: теперь не нужно отключать блоки для серверных конфигураций. Впрочем, даже Intel ничего не изменила, преимущества от новой организации памяти и, вследствие этого, большая пропускная способность должны нивелировать негативное влияние блоков предварительной выборки.

Заключение

Conroe стал серьёзным фундаментом для новых процессоров, и Nehalem построен как раз на нём. Здесь используется такая же эффективная архитектура, но теперь она намного более модульная и масштабируемая, что должно гарантировать успех в разных рыночных сегментах. Мы не говорим о том, что Nehalem революционизировал архитектуру Core, но новый процессор революционизировал платформу Intel, которая теперь стала достойным соответствием для AMD по дизайну, а по реализации Intel успешно обошла конкурента.

|

Нажмите на картинку для увеличения.

Со всеми улучшениями, сделанными на данном этапе (интегрированный контроллер памяти, QPI), неудивительно видеть, что изменения исполнительного ядра не такие значительные. Но возвращение Hyper-Threading можно считать серьёзной новостью, да и ряд небольших оптимизаций тоже должны обеспечить заметный прирост производительности по сравнению с Penryn на равных частотах.

Вполне очевидно, что самый серьёзный прирост будет в тех ситуациях, где основным "узким местом" была оперативная память. Если вы прочитали статью целиком, то наверняка заметили, что именно на эту область инженеры Intel уделили максимум внимания. Кроме добавления встроенного контроллера памяти, который, без сомнения, даст наибольший прирост касательно операций доступа к данным, есть и множество других улучшений, как крупных, так и мелких - новая архитектура кэша и TLB, невыровненный доступ к памяти и блоки предварительной выборки.

Учитывая всю теоретическую информацию, мы с нетерпением ждём, как улучшения отразятся на реальных приложениях после выхода новой архитектуры. Мы посвятим этому несколько статей, так что оставайтесь с нами!

Не так давно на рынке появились процессоры семейства AMD64, в основе которых лежит новое ядро ревизии E. Это ядро, изготавливаемое с использованием технологического процесса с нормами производства 90 нм, а также с применением технологий SOI (Silicon on Insulator) и DSL (Dual Stress Liner) нашло применение сразу в нескольких линейках процессоров от AMD. Сферы применения ядра ревизии E весьма различны. Его можно встретить как в процессорах Athlon 64 и Athlon 64 FX, где оно обозначается кодовыми именами Venice и San Diego; в двухъядерных CPU семейства Athlon 64 X2, где его называют Toledo или Manchester; а также в процессорах Sempron, где это ядро именуется Palermo.

Разрабатывая и доводя до стадии массового производства новые ядра, компания AMD стремится не только к повышению предельных тактовых частот своих процессоров, но и к улучшению их характеристик. Ядро ревизии E стало очередным этапом на этом пути: с его внедрением процессоры Athlon 64 и их производные приобрели новые свойства. Наиболее заметным усовершенствованием стало появление в процессорах AMD поддержки инструкций SSE3, которые имелись в продуктах конкурента со времени начала выпуска CPU с 90 нм ядром Prescott. Кроме этого, традиционной доводке подвергся и интегрированный контроллер памяти.

Тесты показали, что поддержка SSE3 команд даёт очень немного. Приложений, эффективно использующих эти инструкции, на сегодняшний день крайне мало, да и сам набор SSE3 вряд ли может претендовать на звание полноценного подмножества команд.

Поэтому, на этот раз мы решили уделить большее внимание изменениям, внесённым в интегрированный контроллер памяти процессоров с ядром ревизии E. Следует заметить, что в более ранних ядрах своих CPU AMD не только увеличивала производительность контроллера памяти, но и расширяла его совместимость с различными комбинациями различных модулей памяти. Ядро ревизии D, известное в первую очередь благодаря процессорам Athlon 64 с кодовым именем Winchester, в этом плане явилось своеобразным рубежом. Во-первых, в процессорах Winchester по сравнению с предшественниками несколько увеличилась производительность контроллера памяти. Во-вторых, процессоры с ядром Winchester стали способны работать с модулями DDR400 SDRAM, установленными сразу во все четыре слота DIMM на материнской плате. Казалось бы, оптимум достигнут, однако, инженеры AMD посчитали иначе. Процессоры AMD с ядром ревизии E располагают ещё более совершенным контроллером памяти.

Куда же были направлены усилия инженеров на этот раз? Естественно, определенные оптимизации были вновь сделаны для увеличения производительности котроллера памяти. Так, тесты процессоров с ядром Venice продемонстрировали их небольшое превосходство над аналогами с ядром Winchester. Кроме того, снова улучшилась совместимость. Процессоры AMD с ядром ревизии E стали способны нормально функционировать при установке в систему нескольких модулей памяти различной организации и объёма, что, несомненно, значительно упрощает выбор комплектующих для дальнейшего апгрейда. Также, процессоры, в основе которых лежит новое ядро, теперь могут без проблем работать и с четырьмя двухсторонними модулями DDR400 SDRAM. Ещё одним интересным свойством процессоров с ядром ревизии E стало появление новых делителей, задающих частоту памяти. Благодаря этому новые CPU от AMD теперь безо всяких оговорок поддерживают DDR SDRAM, работающую на частотах, превышающих 400 МГц.

реклама

В этом материале мы рассмотрим некоторые из перечисленных выше особенностей интегрированного контроллера памяти ядра ревизии E, ибо, как нам кажется, они того явно заслуживают.Работа с четырьмя двухсторонними модулями DDR400 SDRAM

Интегрированный контроллер памяти процессоров Athlon 64 – достаточно капризный узел. Различные неприятные моменты, связанные с его функционированием стали выясняться с момента появления процессоров с поддержкой двух каналов памяти. Выяснилось, что из-за достаточно высокой электрической нагрузки, которую накладывают модули памяти на контроллер, Athlon 64 имеет определённые проблемы при работе с четырьмя модулями DIMM. Так, при установке в систему на базе Athlon 64 четырёх модулей памяти, CPU может сбрасывать их частоту, увеличивать тайминги или не работать вообще.

Впрочем, справедливости ради следует отметить, что серверный аналог Athlon 64, Opteron, подобных проблем лишён благодаря использованию более дорогих регистровых модулей. Однако, применение таких модулей в настольных системах неоправданно, и поэтому пользователям необходимо мириться с некоторыми ограничениями, возникающими при установке в систему более двух модулей DIMM.

Впрочем, постепенно описанные проблемы всё же решаются. В то время как старые процессоры Athlon 64, основанные на ядрах, производимых по 130 нм технологии, не могли работать с четырьмя двухсторонними модулями DDR400 SDRAM на частоте 400 МГц вообще и снижали их частоту до 333 МГц, современные процессоры с 90 нм ядрами предлагают пользователям несколько лучшие варианты. Уже в ядре ревизии D, известном нам по кодовому имени Winchester, стала возможна работа с четырьмя двухсторонними модулями DDR400 SDRAM, при условии установки тайминга Command Rate в 2T.

В наши дни в цивилизованном мире вы с трудом найдёте человека, который никогда бы не пользовался компьютером и не имел представление о том, что это такое. Поэтому, вместо того чтобы в очередной раз рассказывать обо всем известных частях этой сложной системы, мы расскажем вам о чём-то, что вы ещё не знаете. Мы обсудим и дадим небольшую характеристику контроллерам памяти, без которых работа компьютера была бы невозможна. Если вы хотите вникнуть в систему работы вашего персонального компьютера или ноутбука, то вы обязательно должны знать это. И так, давайте обсудим сегодня, что же такое контроллеры памяти.

Задача, которая стоит перед контроллерами памяти компьютера является очень важной для работы компьютера. Контроллер памяти – это чип, который расположен на материнской плате или на центральном процессоре. Главной функцией, которую выполняет этот крохотный чип, является управление потоками данных, как входящих, так и исходящих. Второстепенной функцией контроллера памяти является увеличение потенциала и работоспособности системы, а так же равномерное и правильное размещение информации в памяти, которое доступно благодаря новым разработкам в области новых технологий.

Размещение контроллера памяти в компьютере зависит от определённых моделей материнских плат и центральных процессоров. В некоторых компьютерах дизайнеры поместили этот чип на северном параллельном присоединении материнской платы, в то время как в других компьютерах они размещены на центральном процессоре типа «die». Те системы, которые рассчитаны на установку контроллера в материнской плате, имеют большое количество новых различных физических гнёзд. Оперативная память, которая используется в компьютерах такого типа, так же имеют новый современный дизайн.

Главная цель использования контроллера памяти в компьютере заключается в том, чтобы система могла считывать и записывать изменения в оперативной памяти, а также обновлять её при каждой загрузке. Это происходит благодаря тому, что контроллер памяти посылает электрические заряды, которые в свою очередь, являются сигналами для выполнения тех или иных действий. Не углубляясь в техническую терминологию, мы можем утвердить тот факт, что контроллеры памяти являются одной из самых важных деталей в компьютере, позволяющих использовать оперативную память, и без которой его работа была бы невозможной.

Контроллеры памяти бывают разных типов. Они различаются на:

- контроллеры памяти с двойной скоростью передачи данных (DDR);

- полностью буферизованные контроллеры памяти (FB);

- двуканальные контроллеры (DC).

Функции, которые могут выполнять контроллеры памяти разных типов, отличаются друг от друга. Например, контроллеры памяти с двойной скоростью передачи данных используются, чтобы передавать данные, в зависимости от увеличения или уменьшения темпа часов памяти. В то время как в двуканальной памяти используется два контроллера памяти параллельно друг от друга. Это позволяет компьютеру увеличить быстродействие системы, создавая больше каналов, но, несмотря на трудности, которые возникают в результате использования кучи проводов, данная система работает довольно эффективно. Однако возникают трудности при создании новых каналов, поэтому данный вид контроллера памяти не безупречен.

Полностью буферизованные контроллеры памяти с другой стороны отличаются от остальных типов контроллеров памяти. В данной технологии используется серийные каналы передачи данных, которые нужны для связи с материнской платой и непохожие на остальные системы схемы оперативной памяти RAM. Преимущество данного типа контроллеров заключается в том, что полностью буферизованные контроллеры памяти уменьшают количество проводов, которые используются в материнской плате, и что позволяет уменьшить затраченное на выполнение задачи время.

Как вы уже убедились, контроллеры памяти очень нужны для стабильной работы компьютера, и разные типы используются для разных целей. Цены на линейки памяти варьируются от очень высоких до очень низких, что зависит от типа и функций, которые выполняет тот или иной контроллер памяти.

Память

Память - это устройство для хранения информации. Она состоит из оперативного и постоянного запоминающего устройств. Оперативное запоминающее устройство называется ОЗУ , постоянное запоминающее устройство - ПЗУ .

ОЗУ- энергозависимая память

ОЗУ предназначена для записи, считывания и хранения программ (системных и прикладных), исходных данных, промежуточных и окончательных результатов. Доступ к элементам памяти прямой. Другое название – RAM (Random Access Memory) память с произвольным доступом. Все ячейки памяти объединены в группы по 8 бит (1 байт) и каждая такая группа имеет адрес, по которому к ней можно обратиться. ОЗУ используется для временного хранения данных и программ. При выключении компьютера, информация в ОЗУ стирается. ОЗУ - энергозависимая память. В современных компьютерах объем памяти обычно составляет от 512 Мбайт до 4 Гигабайт. Современные прикладные программы часто требуют для своего выполнения 128–256, а то и 512 Мбайта памяти, в противном случае программа просто не сможет работать.

Оперативная память может строиться на микросхемах динамического (Dinamic Random Access Memory – DRAM ) или статического (Static Random Access Memory –SRAM ) типа. Статический тип памяти обладает существенно более высоким быстродействием, но значительно дороже динамического. Для регистровой памяти (МПП и КЭШ-память) используются SRAM, а ОЗУ основной памяти строится на базе DRAM-микросхем.

ПЗУ - энергонезависимая память.

В англоязычной литературе ПЗУ называется Read Only Memory, ROM (память только для чтения). Информация в ПЗУ записывается на заводе-изготовителе микросхем памяти, и в дальнейшем изменить ее значение нельзя. В ПЗУ хранится информация, которая не зависит от операционной системы.

В ПЗУ находятся:

Программа управления работой самого процессора

Программы управления дисплеем, клавиатурой, принтером, внешней памятью

Программы запуска и остановки ЭВМ (BIOS – Base Input / Outout Sysytem)

Программы тестирования устройств, проверяющие при каждом включении компьютера правильность работы его блоков (POST -Power On SelfTest)

Информация о том, где на диске находится операционная система .

CMOS - энергонезависимая память

CMOS RAM - энергонезависимая память компьютера. Эта микросхема многократной записи имеет высокую плотность размещения элементов (каждая ячейка имеет размер в 1 байт) и малое потребление энергии – для нее вполне достаточно мощности батареи компьютера. Получила название от технологии создания на основе комплементарных металло-оксидных полупроводников (complementary metal-oxide semiconductor - CMOS). CMOS RAM является собой базу данных для хранения информации о конфигурации ПК. Программа запуска компьютера Setup BIOS используется для установки и хранения параметров конфигурации в CMOS RAM. При каждой загрузке системы для определения ее конфигурации проводится считывание параметров, хранящихся в микросхеме CMOS RAM. Более того, поскольку некоторые параметры запуска компьютера можно менять, то все эти вариации хранятся в CMOS. Программа установки BIOS SETUP при записи сохраняет в ней свою системную информацию, которую впоследствии сама же и считывает (при загрузке ПК). Несмотря на явную связь между BIOS и CMOS RAM, это абсолютно разные компоненты.

Ключевые слова настоящей лекции

контроллеры, чипсет, порты, USB, COM, LPT, BIOS POST, CMOS, Boot, устройства В/В,

(controller - регулятор, управляющее устройство) - устройство управления разнообразными устройствами компьютера.

Чипсет (chipset)

Набор микросхем, спроектированных для совместной работы с целью выполнения набора каких-либо функций. Так, в компьютерах чипсет, размещенный на материнской плате, выполняет роль связующего компонента, обеспечивающего совместное функционирование подсистем памяти, центрального процессора (ЦП), ввода-вывода и других. Матери́нская пла́та (motherboard, MB , также используется название mainboard - главная плата; сленг. мама , мать , материнка ) - это сложная многослойная печатная плата, на которой устанавливаются основные компоненты персонального компьютера (центральный процессор, контроллер ОЗУ и собственно ОЗУ, загрузочное ПЗУ, контроллеры базовых интерфейсов ввода-вывода), чипсет, разъёмы (слоты) для подключения дополнительных контроллеров, использующих шины USB, PCI и PCI-Express.

Северный мост (Northbridge; в отдельных чипсетах Intel, контроллер-концентратор памяти Memory Controller Hub, MCH) - системный контроллер чипсета на материнской плате платформы x86, к которому в рамках организации взаимодействия подключены:

через Front Side Bus - микропроцессор ,

через шину контроллера памяти - оперативная память ,

через шину графического контроллера - видеоадаптер ,

через внутреннюю шину подсоединяется южный мост .

Южный мост (Southbridge; функциональный контроллер; контроллер-концентратор ввода-вывода I/O Controller Hub, ICH). Обычно это одна микросхема на материнской плате, которая через Северный мост связывает с центральный процессором «медленные» (по сравнению со связкой «ЦП-ОЗУ») взаимодействия (например разъёмы шин для подключения периферийных устройств).

AGP (от англ. Accelerated Graphics Port, ускоренный графический порт) - разработанная в 1997 году компанией Intel, специализированная 32-битная системная шина для видеокарты.

PCI (англ. Peripheral component interconnect, дословно - взаимосвязь периферийных компонентов) - шина ввода/вывода для подключения периферийных устройств к материнской плате компьютера.

Ultra DMA (Direct memory access, Прямой доступ к памяти). Разные версии ATA известны под синонимами IDE, EIDE, UDMA, ATAPI; ATA (англ. Advanced Technology Attachment - присоединение по передовой технологии) - параллельный интерфейс подключения накопителей (жёстких дисков и оптических приводов) к компьютеру. В 1990-е годы был стандартом на платформе IBM PC; в настоящее время вытесняется своим последователем - SATA и с его появлением получил название PATA (Parallel ATA).

USB (англ. Universal Serial Bus - «универсальная последовательная шина», произносится «ю-эс-би» или «у-эс-бэ») - последовательный интерфейс передачи данных для среднескоростных и низкоскоростных периферийных устройств в вычислительной технике. Для подключения периферийных устройств к шине USB используется четырёхпроводный кабель, при этом два провода (витая пара) в дифференциальном включении используются для приёма и передачи данных, а два провода - для питания периферийного устройства. Благодаря встроенным линиям питания USB позволяет подключать периферийные устройства без собственного источника питания (максимальная сила тока, потребляемого устройством по линиям питания шины USB, не должна превышать 500 мА).

LPT -порт (стандартного устройства принтера «LPT1» Line Printer Terminal или Line PrinTer) в операционных системах семейства MS-DOS. IEEE 1284 (порт принтера, параллельный порт)

COM -порт («ком-порт» Communication port, Serial port, серийный порт, последовательный порт) - двунаправленный последовательный интерфейс, предназначенный для обмена битовой информацией. Последовательным данный порт называется потому, что информация через него передаётся по одному биту, бит за битом (в отличие от параллельного порта).

PS/2 - разъем, применяемый для подключения клавиатуры и мыши. Впервые появился в 1987 году на компьютерах IBM PS/2 и впоследствии получил признание других производителей и широкое распространение в персональных компьютерах и серверах рабочих групп. серия персональных компьютеров компании IBM на процессорах серий Intel 80286 и Intel 80386, выпускавшаяся с апреля 1987 года. /2 – версия компьютера.

Контроллер памяти теперь неотъемлемая составляющая самого процессора. В процессорах AMD интегрированный контроллер памяти использовался уже более шести лет (до появления архитектуры Sandy Bridge), так что те, кто этим вопросом уже интересовался, достаточное количество информации накопить успели. Однако для процессоров Intel, занимающих куда большую долю рынка (а, следовательно, и для большинства пользователей) актуальным изменение характера работы системы памяти стало только вместе с выходом действительно массовых процессоров компании с интегрированным контроллером памяти.

Перемещение контроллера памяти непосредственно в современные процессоры достаточно сильно сказывается на общей производительности компьютерных систем. Главным фактором тут является исчезновение «посредника» между процессором и памятью в лице «северного моста». Производительность процессора больше не зависит от используемого чипсета и, как правило, вообще от системной платы (т.е. последняя превращается просто в объединительную панель).

Оперативная память следующего поколения, DDR4 SDRAM, привнесла в серверные, настольные и мобильные платформы значительное увеличение производительности. Но достижение новых рубежей быстродействия требует радикальных изменений в топологии подсистемы памяти. Эффективная частота модулей DDR4 SDRAM составит от 2133 до 4266 МГц. Перспективные модули памяти не только быстрее, но и экономичнее своих предшественников. Они используют пониженное до 1,1-1,2 В напряжение питания, а для энергоэффективной памяти штатным является напряжение 1,05 В. Производителям чипов DRAM при изготовлении микросхем DDR4 SDRAM пришлось прибегать к использованию самых передовых производственных технологий.

Массовый переход на использование DDR4 SDRAM планировался на 2015 год, но при этом необходимо иметь в виду, что экстремально высокие скорости работы памяти нового поколения потребовали внесения изменений в привычную структуру всей подсистемы памяти. Дело в том, что контроллеры DDR4 SDRAM смогут справиться лишь с единственным модулем в каждом канале. Это значит, что на смену параллельному соединению модулей памяти в каждом канале придёт чётко выраженная топология точка-точка (каждая установленная планка DDR4 будет задействовать разные каналы). Чтобы гарантировать высокие частоты спецификация DDR4 поддерживает только один модуль на каждый контроллер памяти. Это означает, что производителям потребовалось увеличить плотность чипов памяти и создать более продвинутые модули. В то же время тайминги продолжали расти, хотя время доступа продолжало снижаться.

Компания Samsung Electronics освоила выпуск многоярусных 512-Мбит чипов DRAM по технологии TSV. Именно эту технологию планирует использовать для выпуска DDR4. Таким образом, планируется добиться выпуска относительно недорогих чипов памяти DDR4 очень высокой ёмкости.

Ещё один хорошо известный и уже зарекомендовавший себя способ - использование техники так называемой "разгружающей памяти" - LR-DIMM (Load-Reduce DIMM). Суть идеи состоит в том, что в состав модуля памяти LR-DIMM входит специальный чип (или несколько чипов), буферизирующих все сигналы шины и позволяющих увеличить количество поддерживаемой системой памяти. Правда, не стоит забывать про единственный, пожалуй, но от этого не менее существенный недостаток LR-DIMM: буферизирование неизбежно ведёт к дополнительному увеличению латентности, которая у памяти DDR4 по определению будет и без того немаленькая. Для сегмента серверных и high-end вычислений, где востребован очень большой объём памяти, предлагается совершенно иной выход из ситуации. Здесь предполагается использование высокоскоростной коммутации специальными многовходовыми чипами-коммутаторами.

Компании Intel и Micron совместными усилиями создали новый тип системы хранения данных, который в одну тысячу раз быстрее самой передовой памяти NAND Flash. Новый тип памяти, получивший название 3D XPoint, показывает скорости чтения и записи в тысячу раз превышающие скорость обычной памяти NAND, а также обладает высокой степенью прочности и плотности. Новостное агентство CNET сообщает, что новая память в десять раз плотнее чипов NAND и позволяет на той же физической площади сохранять больше данных и при этом потребляет меньше питания. Intel и Micron заявляют, что их новый тип памяти может использоваться как в качестве системной, так и в качестве энергозависимой памяти, то есть, другими словами, ее можно использовать в качестве замены как оперативной RAM-памяти, так и SSD. В настоящий момент компьютеры могут взаимодействовать с новым типом памяти через интерфейс PCI Express, однако Intel говорит, что такой тип подключения не сможет раскрыть весь потенциал скоростей новой памяти, поэтому для максимальной эффективности памяти XPoint придется разработать новую архитектуру материнской платы.

Благодаря новой технологии 3DXpoint (кросс-поинт) ячейка памяти меняет сопротивление для различения между нулем и единицей. Поскольку ячейка памяти Optane не одержит транзистора, плотность хранения данных в памяти Optane превышает в 10 раз показатели NAND Flash. Доступ к индивидуальной ячейке обеспечивает сочетание определенных напряжений на пересекающихся линиях проводников. Аббревиатура 3D введена поскольку ячейки в памяти расположены в несколько слоев.

Уже в 2017 году технология получила широкое применение и будет использоваться как в аналогах флеш-карт, так и в модулях оперативной памяти. Благодаря новой техноголии, компьютерные игры получат мощнейшее развитие, ведь сложные по объему памяти локации и карты будут загружаться мгновенно. Intel заявляет о 1000-кратном превосходстве нового типа памяти, по сравнению с привычными нам флеш-картами и жесткими дисками. Устройства под брендом Optane будет производить компания Micron с использованием 20-нм техпроцесса. В первую очередь будет произведен выпуск 2.5 дюймовых твердотельных накопителей SSD, но также выйдут диски SSD с другими типоразмерами, дополнительно компания выпустит модули оперативной памяти Оптейн DDR4 для серверных платформ Интел.

Коннекторы и их использование в изготовлении бижутерии Коннекторы RJ применяются с витой парой и телефонными кабелями

Коннекторы и их использование в изготовлении бижутерии Коннекторы RJ применяются с витой парой и телефонными кабелями Как переустановить Windows на ноутбуке: Пошаговая инструкция Переустановка винды на ноутбуке lenovo

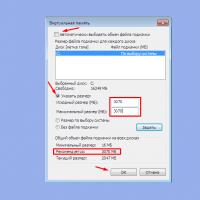

Как переустановить Windows на ноутбуке: Пошаговая инструкция Переустановка винды на ноутбуке lenovo Как увеличить объем оперативной памяти на компьютере

Как увеличить объем оперативной памяти на компьютере Как в фотошопе вырезать и вставить объект Как в фотошопе вырезать изображение и наложить

Как в фотошопе вырезать и вставить объект Как в фотошопе вырезать изображение и наложить Разговаривать по умным часам

Разговаривать по умным часам Как защитить свой компьютер от проникновения хакеров: полезные советы Как защитить компьютер от антивируса

Как защитить свой компьютер от проникновения хакеров: полезные советы Как защитить компьютер от антивируса Что такое blu ray и чем он отличается от обычного формата, а также какое качество изображения предоставляет

Что такое blu ray и чем он отличается от обычного формата, а также какое качество изображения предоставляет