Процессор цифровой обработки сигналов. Процессоры и цифровые сигнальные процессоры (DSP) Применение dsp

Процессор цифровой обработки сигналов (digital signal processor - DSP) - это специализированный программируемый микропроцессор, предназначенный для манипулирования в реальном масштабе времени потоком цифровых данных. DSP-процессоры широко используются для обработки потоков графической информации, аудио- и видеосигналов.

Любой современный компьютер оснащен центральным процессором и только немногие - процессором цифровой обработки сигналов (DSP - digital signal processor). Центральный процессор, очевидно, представляет собой цифровую систему и обрабатывает цифровые данные, поэтому на первый взгляд неясна разница между цифровыми данными и цифровыми сигналами, то есть теми сигналами, которые обрабатывает DSP-процессор.

К цифровым сигналам, в общем случае, естественно отнести все потоки цифровой информации, которые формируются в процессе телекоммуникаций. Главное, что отличает эту информацию, - она не обязательно заносится в память (и поэтому может оказаться недоступной в будущем), следовательно, обрабатывать ее нужно в режиме реального времени.

Число источников цифровой информации практически неограниченно. Так, например, загружаемые файлы в формате MP3 содержат цифровые сигналы, собственно и представляющие звукозапись. В некоторых камкодерах выполняется оцифровка видеосигналов и их запись в цифровом формате. В дорогих моделях беспроводных и сотовых телефонов перед передачей также производится преобразование голоса в цифровой сигнал.

Вариации на тему

DSP-процессоры принципиально отличаются от микропроцессоров, образующих центральный процессор настольного компьютера. По роду своей деятельности центральному процессору приходится выполнять объединяющие функции. Он должен управлять работой различных компонентов аппаратного обеспечения компьютера, таких как дисководы, графические дисплеи и сетевой интерфейс, с тем чтобы обеспечить их согласованную работу.

Это означает, что центральные процессоры настольных компьютеров имеют сложную архитектуру, поскольку должны поддерживать такие базовые функции, как защита памяти, целочисленная арифметика, операции с плавающей запятой и обработка векторной графики.

В итоге типичный современный центральный процессор поддерживает несколько сот команд, которые обеспечивают выполнение всех этих функций. Следовательно, нужен модуль декодирования команд, который позволял бы реализовывать сложный словарь команд, а также множество интегральных схем. Они, собственно, и должны выполнять действия, определяемые командами. Иными словами, типичный процессор в настольном компьютере содержит десятки миллионов транзисторов.

DSP-процессор, напротив, должен быть «узким специалистом». Его единственная задача - изменять поток цифровых сигналов, и делать это быстро. DSP-процессор состоит главным образом из высокоскоростных аппаратных схем, выполняющих арифметические функции и манипулирующих битами, оптимизированных с тем, чтобы быстро изменять большие объемы данных.

В силу этого набор команд у DSP куда меньше, чем у центрального процессора настольного компьютера; их число не превышает 80. Это значит, что для DSP требуется облегченный декодер команд и гораздо меньшее число исполнительных устройств. Кроме того, все исполнительные устройства в конечном итоге должны поддерживать высокопроизводительные арифметические операции. Таким образом, типичный DSP-процессор состоит не более чем из нескольких сот тысяч транзисторов.

Являясь узкоспециализированным, DSP-процессор отлично справляется со своей работой. Его математические функции позволяют непрерывно принимать и изменять цифровой сигнал (такой, как звукозаписи в MP3 или запись разговора по сотовому телефону), не тормозя передачу информации и не теряя ее. Для повышения пропускной способности DSP-процессор оснащается дополнительными внутренними шинами данных, которые обеспечивают более быстрый перенос данных между арифметическими модулями и интерфейсами процессора.

Зачем нужны DSP-процессоры?

Специфические возможности DSP-процессора в части обработки информации делают его идеальным средством для многих приложений. Используя алгоритмы, основанные на соответствующем математическом аппарате, DSP-процессор может воспринимать цифровой сигнал и выполнять операции свертки для усиления или подавления тех или иных свойств сигнала.

В силу того что в DSP-процессорах значительно меньше транзисторов, чем в центральных процессорах, они потребляют меньше энергии, что позволяет использовать их в продуктах, работающих от батарей. Крайне упрощается и их производство, поэтому они находят себе применение в недорогих устройствах. Сочетание низкого энергопотребления и невысокая стоимость обусловливает применение DSP-процессоров в сотовых телефонах и в роботах-игрушках.

Впрочем, спектр их применения этим далеко не ограничивается. В силу большого числа арифметических модулей, наличия интегрированной на кристалле памяти и дополнительных шин данных часть DSP-процессоров могут использоваться для поддержки многопроцессорной обработки. Они могут выполнять сжатие/распаковку «живого видео» при передаче по Internet. Подобные высокопроизводительные DSP-процессоры часто применяются в оборудовании для организации видеоконференций.

Внутри DSP

Приведенная здесь диаграмма иллюстрирует строение ядра процессора Motorola DSP 5680x. Раздельные внутренние шины команд, данных и адресов способствуют резкому повышению пропускной способности вычислительной системы. Наличие вторичной шины данных позволяет арифметическому устройству считать два значения, перемножить их и выполнить операцию накопления результата за один такт процессора.

Нечаянно наткнулся на видео с "Чип и Дип" #1 Цифровая обработка звука ADAU1701 | Открытый проект | Начало

И тут "накрыло" всякими воспоминаниями по поводу этой темы. Решил проверить, что творится в наше время на этом фронте, нашёл что много хорошего и интересного.

Качество обработки значительно выросло, цена значительно упала и звуковые DSP (Digital Signal Processing) уже стучатся к нам в дом! :)

В данном видео рассматривается чип SigmaDSP ADAU1701 и я решил посмотреть что можно с ним сотворить и был сильно впечатлён возможностями.

на русском можно о них почитать (). Для меня данный DSP позволяет построить нормальную акустическую систему с внешним кроссовером. Возможностей у системы невообразимо больше, чем мои потуги. Она позволяет запрограммировать себя полному новичку в программировании, но понимающему звуковые компоненты и как они работают: фильтры; кроссоверы; эквалайзеры и т.д. и т.п. Эти знания нужны, чтобы всё это настраивать

Вот так выглядит пример проекта в программе обслуживающей и программирующей DSP:

Как видите почти никаких "цифровых значений", а всё обзывается "по-звуковому".

Конечно его АЦП и ЦАП"ы далеко не Hi-End, а средний Hi-Fi, но для дома этого качества достаточно, а возможности очень велики. Очень хорошо, что DSP имеет двойную точность вычислений (56-бит) и она установлена по умолчанию.

Нуу... маленькие/неполные дифирамбы пропели, теперь реальность.

Плата есть в разных исполнениях:

Вариант 1

. Полная тестовая плата от производителя стоит ~12-15 тыщ рублей

и позволяет вытворять всё что угодно. ИМХО самое большое преимущество перед остальными - это полный SPDIF, т.е. и цифровой вход и цифровой выход результатов. Также позволяет делать отладку алгоритмов "на лету". Заказывать "за бугром" с сайта производителя.

Вариант 2

. Это слегка обрубленный макет от МастерКит - набор BM2114dsp . У него все входы/выходы аналоговые, но отладка всё также "на лету".

Стоимость 4900 руб

.

Вариант 3

. Это максимально упрощённый вариант использования DSP от "Чип и Дип" их лаборотории "Электронный войска".

Комплект называется Digital Signal Processors RDC2-0027v1, Модуль цифровой обработки звука на SigmaDSP ADAU1701, SigmaStudio

Это вариант с отсутствием программирования "на лету". Создаёшь бинарник, конвертируешь и "заливаешь" с помощью "свистка" в ERROM платы. Отнимает это немного времени, но отнимает, и требует понимания процесса. :)

Стоимость платы 950 рубликов

.

Да, уточню, плата после программирования работает как независисмое устройство!!! Т.е. ПК вечно не нужен! И к плате можно подключать "крутилки" (энкодеры); кнопочки и т.д., т.е. внешних методов регулировки достаточно, не обязательно на каждый чих лезть в код DSP.

Выбор за вами...

Теперь касаемо моих хотелок из прошлого. Одна из больших проблем пассивных фильтров - это фазовые искажения и чем больше крутизна спада фильтров, тем больше фазовые искажения. Из-за них возникает множество призвуков от которых чрезвычайно сложно избавится и трудно согласовывать разные частотные диапазоны.

Данные цифровые фильтры этим не страдают и позволяют вытворять многое для согласования полос среза. Но возникает необходимость использовать вместо одного усилителя - три, по одному на каждый частотный диапазон (раз колонка 3-х полосная, то полос 3 и усилителей получается 3). Конечно, их можно оптимизировать по мощности (допустим в моём случае выйдет НЧ - 30Вт; СЧ - 20Вт; ВЧ - 10Вт), но тут на возможности и любителя, думаю унификация победит. :)

Под конец множество видео

Пример, как самому сварганить работу по "цифре"

Парень собирает монстра на двух DSP

Не так давно благодаря большому прогрессу в области обработки звука и компьютерных технологий в наше сознание твердо вошло такое понятие как DSP - Digital Signal Processing (Цифровая Обработка Сигнала). Цифровая обработка сигнала - это область техники, занимающаяся реализацией вычислительных алгоритмов в реальном времени. DSP говорит нам о возможности того или иного трансивера реализовывать этот сервис через свои технические возможности. Некоторые современные трансиверы имеют цифровую обработку как на прием, так и на передачу. Можно с уверенностью сказать, что цифровая обработка обеспечивает качество, которое соответствует новым технологиям и времени, в котором мы живем.

Цифровая обработка применительно к радиолюбительству чаще всего применяется при обработке сигнала из эфира, с целью обеспечения более качественного приема, устранения помех, сопровождающих передачу корреспондента. Это осуществляется при работе любыми видами связи, включая цифровые. Для этой цели часто используют компьютер со встроенной звуковой картой (ЗК) и соответствующее программное обеспечение. Однако в реальном времени сигнал обрабатывается с задержкой, и если в режиме приема это еще терпимо, то при передаче - нет.

Работая SSB и используя аппаратно-программные возможности компьютера в обработке сигнала с микрофона, который подключен к звуковой карте компьютера (с последующей подачей НЧ- сигнала на балансный модулятор трансивера), задержка очень существенна. Речь идет не просто об усилении сигнала с микрофона до определенного уровня с помощью ЗК, а об использовании специальных программ обработки сигнала в реальном времени. Ситуация еще более обостряется при работе такими цифровыми видами как Amtor, Pactor, Packet, когда одновременно программно компьютер используется, скажем, как Notch-фильтр и вместе с имеющимся на станции TNC-контроллером он обеспечивает перечисленные виды работ. Задержка в обработке сигнала в компьютере в таких случаях недопустима. Для того чтобы избавиться от этой проблемы, применяют звуковую карту Audigy-2 (например, AUDIGY-2 24 bit 96 kHz).

Также эта звуковая карта имеет аппаратно встроенный процессор эффектов, что позволяет, используя программно-аппаратные возможности, производить обработку сигнала в реальном времени на достаточно высоком уровне, т.е. в режиме передачи, например, в телефонных видах работ - SSB, AM, ЧМ - иметь хороший эквалайзер, компрессор, лимитер, а в режиме приема - Notch-фильтр, экспандер или что-либо другое.

Все это возможно даже при наличии персонального компьютера с процессором Pentium 200…500 МГц, хотя применение более мощных машин приветствуется, поскольку появляются еще большие возможности обработки сигнала с применением программного обеспечения - Plug In и соответствующих программ, алгоритм обработки которых требует более высокой производительности компьютера.

В этом случае современные технологии позволяют не применять внешние дорогостоящие приборы цифровой обработки, а в той или иной степени имитировать их работу, используя для этого вычислительные мощности центрального процессора компьютера и звуковой карты. Однако зто возможно при действительно очень высоких ресурсах компьютера. Применяя эти технологии, остается лишь установить узел стыковки - интерфейс - между трансивером и компьютером и с успехом использовать возможности последнего.

Отдавая должное цифровой обработке сигнала в трансивере или с помощью компьютера, радиолюбители также используют внешние блоки DSP обработки. Это относительно новое направление в радиолюбительстве.

Речь идет о цифровой обработке сигнала с применением высокотехнологичного, современного оборудования, применяемого в радиовещательных и музыкальных студиях, обеспечивающего абсолютно профессиональное качество и естественность звучания. Это высококачественные микшерные пульты, а также всевозможные аналого-цифровые многополосные (чаще параметрические) эквалайзеры, системы шумоподавления - Noise Gate, компрессоры, лимитеры, процессоры мультиэффектов, позволяющие получить различные алгоритмы звуковой обработки.

Следует отметить, что DSP - это общее понятие. Можно иметь DSP эквалайзер, компрессор, другие устройства и даже предусилитель микрофона. Иметь функцию DSP в трансиве- ре - это одно, иметь целую студию DSP-оборудования - это совершенно другие возможности. Это справедливо, если в обоих случаях упомянутая обработка осуществляется по низкой частоте.

Известные фирмы-производители DSP оборудования - Behringer www.behringer.com, Alesis www.alesis.com и другие - имеют огромный его перечень, и многое из него с успехом может быть применено радиолюбителями.

Каждое из этих устройств выполняет свою задачу и, как правило, содержит в своих двух каналах прецизионные 24-битовые АЦП и ЦАП (аналогово-цифровые и цифро-аналоговые преобразователи), работающие на профессиональной частоте дискредитации и имеющие диапазон рабочих частот 20 Гц…20 кГц.

Краткая справка

Аналогово-цифровой и цифро-аналоговый преобразователи. Первый преобразует аналоговый сигнал в цифровое значение амплитуды, второй выполняет обратное преобразование.

Принцип работы АЦП состоит в измерении уровня входного сигнала и выдаче результата в цифровой форме. В результате работы АЦП непрерывный аналоговый сигнал превращается в импульсный, с одновременным измерением амплитуды каждого импульса. ЦАП получает на входе цифровое значение амплитуды и выдает на выходе импульсы напряжения или тока нужной величины, которые расположенный за ним интегратор (аналоговый фильтр) превращает в непрерывный аналоговый сигнал.

Как всякое новое (особенно требующее вложения денег) направление, оно имеет своих сторонников и противников. Для достижения высокого уровня качества требуется применение на передачу более широкого фильтра в SSB-формирователе трансивера - 3 кГц, а не 2,4 кГц или 2,5 кГц,но это не выходит за рамки регламента радиолюбительской связи в части применяемого оборудования.

Сегодня отвергать право на существование направления в обработке звука с помощью добавочных устройств может только ленивый, завистливый или тот, кто не приветствует прогресс и новые технологии.

«Hi-Fi Audio in SSB» - высокое качество обработки НЧ-сигнала в SSB, или «Extended SSB» - расширенное SSB - фразы, часто слышимые и частично объясняющие уже более чем 10-летнюю активность радиолюбителей со всего мира на частоте 14178 кГц.

Здесь находится «круглый стол» любителей студийных сигналов и способов их получения. Это «круглый стол», который не имеет времени проведения. Работа ведется практически круглые сутки. В мире насчитывается чуть более 100 активных радиолюбителей, использующих эти технологии Их не очень беспокоят QRM, тк они уже достигли значительных успехов в оснащении своих станций и имеют не только высокого класса трансиверы усилители мощности (часто класса High Power), но и, что самое важное, эффективные направленные антенны

Многие слышат при практически любом прохождении, а иногда и при его отсутствии Билла, W2ONV, из Нью-Джерси - старейшего радиолюбителя и большого специалиста в области обработки звука с помощью внешних DSP-устройств Имея мощность 1,5 кВт (максимально разрешенную в США) и два сфазированных четырехэлементных волновых канала, он в течение уже многих лет практически всегда слышен в Европе на частоте 14178 кГц Люди, работающие на этом «круглом столе» - разного возраста, в основном, от 30 до 80 лет, причем тон в работе в большей степени задают радиолюбители старшей возрастной группы И это не дань уважения старшему поколению, это констатация факта Именно они имеют большие успехи в области цифровой обработки, поскольку владеют достаточными знаниями и более серьезным оборудованием.

Радиолюбители на «14178» - выдержанные и спокойные, полностью увлеченные своим делом Начинающим коллегам- энтузиастам всегда рады и оказывают им всяческое содействие Большой вклад в развитие обработки звука вносят сами же радиолюбители, размещая на своих WEB-страницах в Интернете полезную информацию Многие согласятся, что огромный вклад в развитие этого направления внес John, NU9N, создавший сайт в Интернете (www.nu9n.com), где он разместил практически учебник по применению внешних устройств цифровой обработки, последовательности их подключения (очень важный вопрос) установке параметров На сайте NU9N можно также скачать образцы DSP-сигналов многих радиолюбителей Слушать их достаточно интересно.

К сожалению, в количественном плане станции из бывшего Союза представлены на 14178 кГц очень слабо - Василий, ER4DX, Игорь, EW1MM, Сергей, EW1DM, Сергей, RW3PS, Виктор, RA9FIF и Олег, RV3AAJ (других данных нет) Сказывается отсутствие лишних финансов на приобретение аудио- оборудования, а также менталитет людей - когда нет времени и средств всем этим заниматься, значит, это плохо, значит, это не нужно Очевидно, следует остановиться на том, что все направления в радиолюбительстве имеют право на жизнь, будь то соревнования, работа QRP (или QRO), DX’ing И даже отсутствие у некоторых знаний азбуки Морзе, иностранного языка и многого другого - это ведь тоже «направление», и мы, увы, к этому уже вроде как и начинаем привыкать.

Пожелаем же «молодым’ (10 лет для радио - срок небольшой) успехов в их нелегком хобби, а всех кто уже достиг результатов в других областях, приглашаю присоединиться к сообществу любителей студийных сигналов, в конце концов, интереснее дебюта ведь ничего нет.

Данная статья открывает серию публикаций, посвященных многоядерным цифровым сигнальным процессорам TMS320C6678. В статье дается общее представление об архитектуре процессора. Статья отражает лекционно-практический материал, предлагаемый слушателям в рамках курсов повышения квалификации по программе «Многоядерные процессоры цифровой обработки сигналов C66x фирмы Texas Instruments», проводимых в Рязанском государственном радиотехническом университете.

Цифровые сигнальные процессоры TMS320C66xх строятся по архитектуре KeyStone и представляют собой высокопроизводительные многоядерные сигнальные процессоры, работающие как с фиксированной, так и с плавающей точкой. Архитектура KeyStone – это разработанный фирмой Texas Instruments принцип изготовления многоядерных систем на кристалле, позволяющий организовывать эффективную совместную работу большого числа ядер DSP- и RISC-типов, акселераторов и устройств периферии с обеспечением достаточной пропускной способности внутренних и внешних каналов пересылки данных, основой чего являются аппаратные компоненты: Multicore Navigator (контроллер обмена данными по внутренним интерфейсам), TeraNet (внутренняя шина пересылки данных), Multicore Shared Memory Controller (контроллер доступа к общей памяти) и HyperLink (интерфейс с внешними устройствами на внутрикристальной скорости).

Архитектура процессора TMS320C6678 , наиболее высокопроизводительного процессора в семействе TMS320C66xх, изображена на Рисунке 1. Архитектура может быть разбита на следующие основные компоненты:

- набор операционных ядер (CorePack);

- подсистема работы с общей внутренней и внешней памятью (Memory Subsystem);

- периферийные устройства;

- сетевой сопроцессор (Network Coprocessor);

- контроллер внутренних пересылок (Multicore Navigator);

- служебные аппаратные модули и внутренняя шина TeraNet.

Рисунок 1. Общая архитектура процессора TMS320C6678

Процессор TMS320C6678 работает на тактовой частоте 1.25 ГГц. В основе функционирования процессора лежит набор операционных ядер С66х CorePack, количество и состав которых зависят от конкретной модели процессора. ЦСП TMS320C6678 включает в свой состав 8 ядер DSP-типа. Ядро является базовым вычислительным элементом и включает в свой состав вычислительные блоки, наборы регистров, программный автомат, память программ и данных. Память, входящая в состав ядра, называется локальной.

Кроме локальной памяти, есть память общая для всех ядер – общая память многоядерного процессора (Multicore Shared Memory – MSM). Доступ к общей памяти осуществляется через подсистему управления памятью (Memory Subsystem), которая также включает интерфейс внешней памяти EMIF для обмена данными между процессором и внешними микросхемами памяти.

Сетевой сопроцессор повышает эффективность работы процессора в составе различного рода телекоммуникационных устройств, реализуя аппаратно типовые для данной сферы задачи обработки данных. В основе работы сопроцессора лежат акселератор пакетной передачи данных (Packet Accelerator) и акселератор защиты информации (Security Accelerator). В спецификации на процессор перечислен набор протоколов и стандартов, поддерживаемых данными акселераторами.

Периферийные устройства включают:

- Serial RapidIO (SRIO) версии 2.1 – обеспечивает скорость передачи данных до 5 GBaud на линию при числе линий (каналов) – до 4;

- PCI Express (PCIe) версии Gen2 – обеспечивает скорость передачи данных до 5 GBaud на линию при числе линий (каналов) – до 2;

- HyperLink – интерфейс внутренней шины, позволяющий коммутировать процессоры, построенные по архитектуре KeyStone, напрямую друг с другом и осуществлять обмен на внутрикристальной скорости; скорость передачи данных – до 50 Gbaud;

- Gigabit Ethernet (GbE) обеспечивает скорости передачи: 10/100/1000 Mbps и поддерживается аппаратным акселератором сетевых коммуникаций (сетевым сопроцессором);

- EMIF DDR3 – интерфейс внешней памяти типа DDR3; имеет разрядность шины 64 бита, обеспечивающую адресуемое пространство памяти до 8 Гбайт;

- EMIF – интерфейс внешней памяти общего назначения; имеет разрядность шины 16 бит и может использоваться для подключения 256MB NAND Flash или 16MB NOR Flash;

- TSIP (Telecom Serial Ports) – телекоммуникационный последовательный порт; обеспечивает скорости передачи до 8 Mбит/с на одну линию при числе линий – до 8;

- UART – универсальный асинхронный последовательный порт;

- I2C – шина внутренней связи;

- GPIO – ввод-вывод общего назначения – 16 выводов;

- SPI – универсальный последовательной интерфейс;

- Таймеры (Timers) – используются для генерации периодических событий.

- модуль отладки и трассировки (Debug and Trace) – позволяет получать отладочным инструментальным средствам доступ к внутренним ресурсам работающего процессора;

- загрузочное ПЗУ (boot ROM) – хранит программу начальной загрузки;

- аппаратный семафор (semaphore) – служит для аппаратной поддержки организации совместного доступа параллельных процессов к общим ресурсам процессора;

- модуль управления питанием – реализует динамическое управление режимами питания компонентов процессора с целью минимизации энергозатрат в моменты, когда процессор работает не в полную мощь;

- схема ФАПЧ – формирует внутренние тактовые частоты процессора из внешнего опорного тактирующего сигнала;

- контроллер прямого доступа в память (EDMA) – управляет процессом пересылки данных, разгружая операционные ядра ЦСП и являясь альтернативой Multicore Navigator.

Основой функционирования многоядерного процессора TMS320C66xх с позиции высокоскоростного обмена данными между всеми многочисленными компонентами процессора, а также внешними модулями, служит внутренняя шина TeraNet.

В следующей статье будет подробно рассмотрена архитектура операционного ядра C66x.

1. Multicore Programming Guide / SPRAB27B - August 2012;

2. TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor Data Manual / SPRS691C - February 2012.

Цифровая обработка сигналов DSP (digital signal processor)

Особенности DSP

DSP представляют собой специализированные процессоры для приложений, требующих интенсивных вычислений.

Если ближе рассмотреть, к примеру, процесс операции умножения двух чисел с сохранением результата в традиционных микропроцессорах, то можно увидеть как расходуется машинное время: сначала происходит выборка команды (адрес команды выставляется на шину адреса), затем первого операнда (адрес операнда выставляется на шину адреса), затем операнд переносится в аккумулятор, далее происходит выборка второго операнда и т.д. Ускорение этого процесса в процессоре общего назначения невозможна из-за наличия единственной шины адреса и единственной шины данных, а также единственного банка данных. Ввиду этого все операции по извлечению операндов из памяти, выборки команды и сохранения операнда производится последовательно с использованием одной и той же шины данных и шины адреса. Кроме того, если рассмотреть операцию циклического суммирования арифметического ряда, то можно видеть что здесь непроизводительные затраты времени связаны с запоминанием адреса первой команды цикла, с проверкой условия цикла (счетчика) и возвратом к первой команде. Также большие непроизводительные затраты существуют при операциях перехода к подпрограмме и возврата (запись и восстановление значений регистров из стека) и при многих других операциях. Если при этом учесть огромное количество математических операций при выполнении цифровой обработки сигналов, то станет ясно, что неизбежны весьма чувствительные потери в точности вычисления при округлениях, которые не могут не сказаться на общем результате. Это происходит по причине одинаковой разрядности всех регистров процессоров общего назначения.

При цифровой обработке сигналов все эти затраты недопустимы. С целью преодоления этого недостатка процессоров общего назначения и были разработаны процессоры цифровых сигналов (DSP - Digital Signal Processor).

Трехшинная Гарвардская архитектура

Ее особенность состоит прежде всего в том, что в отличии от привычных нам двух шин: шины адреса и шины данных, а также одного банка памяти, DSP имеет как минимум 6-7 различных шин и 2-3 банка памяти. Эта особенность имеет своей целью максимально ускорить выполнение операции умножения с сохранением результата, которая, несомненно, является наиболее употребляемой и ресурсоемкой при цифровой обработке сигналов. Архитектура DSP позволяет за один машинный цикл произвести:

- выборку команды посредством шины адреса программ и шины данных программ;

- выборку двух операндов для операции умножения посредством двух шин адреса данных;

- занесение операндов в аккумуляторы посредством двух шин данных;

- операцию умножения;

- сохранить результат в аккумуляторе.

Таким образом, трехшинная Гарвардская архитектура позволяет выполнить практически любую операцию за один машинный цикл.

B качестве примера эффективности использования DSP при реализации алгоритмов цифровой обработки сигналов можно привести следующий факт: время выполнения комплексного 1024-точечного преобразования Фурье составляет 20 мс для 486DX2 66 МГц (32-разрядный) и 3.23 mc для 24-разрядного 33 МГц DSP56001 фирмы Motorola или 3.1 мс для 32- разрядного 33 МГц DSP TMS320C30 с плавающей арифметикой фирмы Texas Instruments.

Однако, как уже упоминалось, процессоры цифровой обработки сигнала имеют отличием не только высокую производительность, измеряемую в быстроте выполнения операций умножения/аккумуляции (MIPS - миллионы команд в секунду), но и такие характеристики, как последовательность выполнения программ, арифметических операций и адресации памяти, позволяющие сократить до минимума непроизводительные затраты времени. В целом DSP отличается от других типов микропроцессоров и микроконтроллеров по следующим пяти основным признакам:

- Быстрая арифметика.

DSP - процессор должен осуществлять выполнение за один цикл операций умножения, умножения с аккумуляцией, циклический сдвиг, а также стандартные арифметические и логические операции.

- Расширенный динамический объем для операции умножения/аккумуляции.

Операция вычисления суммы некой последовательности значений является фундаментальной для алгоритмов, реализуемых на DSP. Защита от переполнения необходима для избежания потери данных.

- Выборка двух операндов за один цикл.

Очевидно, что для большинства операций, выполняемых DSP, необходимы два операнда. Таким образом, для достижения максимального быстродействия процессор должен быть способен производить одновременную выборку двух операндов, что требует также наличия гибкой системы адресации.

- Наличие аппаратно реализованных циклических буферов(встроенных и внешних).

Широкий класс алгоритмов, реализуемых на DSP требует использования циклических буферов. Аппаратная поддержка циклического возврата указателя адреса или модульная адресация уменьшает непроизводительные затраты процессорного времени и упрощает реализацию алгоритмов.

- Организация циклов и ветвлений без потери в производительности.

Алгоритмы DSP включают очень много повторяющихся операций, которые могут быть реализованы в виде циклов. Возможность организации последовательности выполнения программы кодов в цикле без потери производительности отличают DSP от других процессоров. Аналогично, потеря времени при выполнении операции ветвления по условию также недопустима при цифровой обработке сигналов.

Не следует, однако, думать, что DSP могут полностью заменить процессоры общего назначения. Как правило, процессоры цифровых сигналов имеют упрощенную систему команд, не позволяющие выполнить операции, не связанные с математическими вычислениями с такой же эффективностью, как и процессоры общего назначения. Попытка же сочетания в одном процессоре мощность при математических вычислениях и гибкость при операциях другого рода приводит к неоправданному повышению себестоимости. Поэтому DSP используют чаще в виде сопроцессоров (математических, графических, акселераторов и т.д.) при главном процессоре либо в качестве самостоятельного процессора, если этого достаточно.

DSP фирмы Motorola

Фирмой Motorola в настоящее время выпускается три семейства Цифровых Процессоров Сигналов. Это серии DSP56100, DSP56000 и DSP96000. Все микросхемы приведенных серий основываются на архитектуре DSP56000 и различаются разрядностью (16, 24, 32 бит соответственно) и некоторыми встроенными устройствами. Таким образом достигается совместимость микросхем всех трех семейств снизу вверх. Все DSP фирмы Motorola построены по идентичной трехшинной Гарвардской архитектуре, описанной ранее, с большим количеством составных частей, портов, контроллеров, банков памяти и шин, работающих параллельно с целью достижения максимального быстродействия.

Передача данных

происходит по двунаправленным шинам данных (одной для DSP56100 (XDB) и двум для DSP56000 и DSP96000 (XDB и YDB)), шине данных программ (PDB) и общей шине данных (GDB). Кроме того, у DSP96000 присутствует отдельная шина прямого доступа к памяти (DDB). Передача данных между шинами происходит через внутреннее устройство управления шинами.

Адресация

осуществляется по двум однонаправленным шинам: шине адреса данных и шине адреса программ.

Блок манипуляции битами

позволяет гибко управлять состоянием любого бита в регистрах и ячейках памяти. Наличие такой возможности является преимуществом по отношению к DSP других пользователей.

Арифметико-логическое устройство (АЛУ)

выполняет все арифметические и логические операции и имеет в своем составе входные регистры, аккумуляторы, регистры расширения аккумуляторов (8-битные, допускающие 256 переполнений без потери точности), параллельный одноцикловой блок умножения с сохранением (МАС), а так же сдвиговые регистры.Гибкая система команд позволяет выполнить АЛУ за один цикл команды умножения, умножения с сохранением результата, суммирования, вычитания, сдвига и логические операции. Характерной особенностью DSP фирмы Motorola является возможность сдваивания входных регистров АЛУ и увеличения таким образом разрядности обрабатываемых чисел. Еще одной важной особенностью является наличие операции деления, зачастую отсутствующей у других производителей и заменяемой операцией умножения на обратное число, что приводит к потере точности.

Блок формирования адреса

выполняет все вычисления, связанные с определением адресов в памяти. Этот блок работает независимо от остальных блоков процессора. За один цикл могут производиться две операции считывания из памяти или одна операция записи. DSP фирмы Motorola обладают чрезвычайно мощной мощной системой адресации, позволяющей производить практически любые манипуляции с данными за одну команду. Это важная особенность выгодно отличает DSP, выпускаемые фирмой, от аналогов. Адресация по модулю удобна для организации кольцевых буферов без проверки выхода за границу, что позволяет избегать непроизводительных затрат времени. Возможность адресации с инверсией значащих битов облегчает реализацию БПФ.

Блок

управления

выполнением

программ

содержит 6 регистров, среди которых Указатель адреса цикла

и Счетчика циклов

, позволяющие организовать аппаратную поддержку организации циклов в DSP фирмы Motorola, при которой не тратятся дополнительные машинные циклы на проверку условия выхода из цикла и изменения счетчика цикла. В команде организации цикла DO явно указывается количество повторений.

Системный стек представляет из себя отдельную часть из 15 слов ОЗУ, и может хранить информацию о 15 прерываниях, 7 циклах или 15 выходах в подпрограмму. Данные из стека читаются за один цикл уменьшая таким образом непроизводительные затраты времени процессора.

Главной отличительной особенностью DSP фирмы Motorola является наличие у всех микросхем внутрикристального эмулятора

, позволяющие производить отладку программ без использования дополнительных аппаратных средств. Таким образом нет необходимости в покупке дорогостоящих отладочных средств. Эмулятор позволяет производить запись/считывание регистров и ячеек памяти, установку точек останова, пошаговое выполнение программ и другие действия посредством подачи команд по 4- проводной шине.

Для снижения потребления энергии в моменты, когда не производится вычисления, предусмотрены два режима с пониженным энергопотреблением: STOP

и WAIT.

Для работы совместно с другими процессорами и каналами прямого доступа к памяти предусмотрен встроенный HOST-интерфейс.

Обладая всеми вышеперечисленными свойствами, необходимыми для цифровой обработки сигналов, DSP фирмы Motorola имеют чрезвычайно мощную и гибкую систему команд, позволяющую пользователю удобно и эффективно работать с процессорами.

Семейство DSP96000

Семейство DSP DSP96000 имеет 32-битную архитектуру и поддерживает операции с плавающей точкой. Микросхемы семейства предназначены для компьютерных систем Multimedia. DSP этой серии могут работать и как самостоятельные микросхемы, и через два независимых 32-битных порта могут последовательно обмениваться данными с другими процессорами.

Микросхемы семейства имеют в своем составе 6 банков памяти, 8 шин и 4 автономных вычислительных блока: АЛУ, блок управления программой, двойной блок генерации адреса и встроенный двухканальный контроллер прямого доступа к памяти.

Характеристики микросхем семейства DSP96000:

- 49.5 MIPS при 40 МГц

- 60 MFLOPS при 40 МГц, цикл 50 нс

- 32-битная организация

- 2 банка памяти данных ОЗУ 512х32 бит

- 2 банка памяти данных ПЗУ 512х32 бит

- ОЗУ программ 1024х32 бит

- загрузочное ПЗУ объемом 56 байт

- адресуемая внешняя память 2х232 32-битных слов памяти данных и программ

- встроенный эмулятор

- 2 канала прямого доступа к памяти

- 2 канала обмена с внешними процессорами

- корпус с 223 выводами в корпусе PGA или QFP

DSP фирмы Texas Instruments

DSP этой фирмы представлены следующими микропроцессорами: TMS 32010, TMS 320C20, TMS 320C25, TMS 320C30, TMS 320C40, TMS 320C50.

Особенности архитектуры ТMS320C25

Архитектура TMS320C2x основана на архитектуре TMS32010 - первом члене микропроцессорного семейства DSP. Кроме того, набор его команд перекрывает набор команд микропроцессора TMS32010, что сохраняет программную совместимость снизу вверх.

Микропроцессор TMS320C2x имеет один аккумулятор и использует Гарвардскую архитектуру в которой память данных и память программ разнесены в разные адресные пространства. Это позволяет полностью перекрыть во времени вызов и выполнение команды. Система команд включает команды обмена данными между двумя областями памяти. Вне микропроцессора пространства памяти данных и программ объединены на одну и ту же шину для того, чтобы максимально увеличить диапазон адресов в обеих областях памяти и одновременно максимально уменьшить количество выводных контактов. Внутри микропроцессора пространства программ и данных выведены на разные шины, чтобы увеличить мощность процессора и скорость выполнения программ.

Повышенная гибкость конструкции системы обеспечивается расположенными на кристалле двумя большими блоками памяти RAM, один из которых может использоваться и как память программ и как память данных. Большинство команд процессора выполняются за один машинный цикл с использованием как внешней памяти программ с быстрой выборкой, так и с использованием внутренней памяти RAM. Гибкость микропроцессора TMS320C2x предусматривает также подключение медленной внешней памяти или периферийных устройств, используя сигнал READY; но в этом случае команды выполняются за несколько машинных циклов.

Организация памяти

На кристалле TMS32020 находится 544 16-разрядных слова памяти RAM, из которых 288 слова (блоки B1 и B2) всегда отведены под данные, а 256 слов (блок B0) в разных конфигурациях процессора могут использоваться либо как память данных, либо как память программ. TMS320C25 кроме того обеспечен маскируемым ПЗУ (ROM), объемом 4К слов, а TMS320E25 - памятью 4К слов с ультрафиолетовым стиранием EPROM.

TMS320C2x обеспечен тремя разделенными адресными пространствами - для памяти программ, для памяти данных и для устройств ввода/вывода, как показано на рис. 6.5. Эти пространства вне кристалла различаются при помощи сигналов -PS, -DS, -IS (для пространств программы, данных, ввода/вывода соответственно). Блоки памяти B0, B1, B2, расположенные на кристалле, охватывают в сумме 544 слова памяти с произвольным доступом (RAM). RAM блок B0 (256 слов) располагается на 4 и 5 страницах памяти данных, если он отведен под данные, или по адресам >FF00 - >FFFF, если он является частью памяти программ. Блок B1 (только для данных) располагается на 6 и 7 страницах, а блок B2 занимает старшие 32 слова 0 страницы. Отметим, что оставшуюся часть 0 страницы занимают 6 адресуемых регистров и резервная область; 1 - 3 страницы также представляют собой резервную область. Резервные области нельзя использовать для хранения информации, при чтении их содержимое не определено.

Внутренняя память программ (ROM), расположенная на кристалле процессора может быть использована в качестве младших 4К слов памяти программ. Для этого на контакт MP/*MC должен быть подан сигнал низкого уровня. Для запрещения использования внутренней области ROM на MP/*MC надо подать высокий уровень.

Внешняя память и интерфейс ввода/вывода

Микропроцессор TMS32020 поддерживает широкий диапазон интерфейсных систем. Адресное пространство данных, программ и ввода/вывода обеспечивает сопряжение с памятью и внешними устройствами, что увеличивает возможности системы. Интерфейс локальной памяти состоит из:

- 16-ти разрядной шины данных (D0-D15);

- 16-ти разрядной шины адреса (A0-A15);

- адресных пространств данных, программ и ввода/вывода выбираемых сигналами (*DS, *PS и *IS);

- различных сигналов управления системой.

Сигнал R/*W управляет направлением передачи, а сигнал *STRB управляет передачей.

Пространство ввода/вывода содержит 16 портов для вводы и 16 портов для вывода. Эти порты обеспечивают полный 16-разрядный интерфейс со внешними устройствами по шине данных. Одноразовый ввод/вывод с помощью команд IN и OUT выполняется за два командных цикла; однако использование счетчика повторений снижает время одного обращения к порту до 1-го цикла.

Использование ввода/вывода упрощается тем, что ввод/ вывод осуществляется также, как и обращение к памяти. Устройства ввода/вывода отображаются в адресном пространстве ввода/вывода, используя внешние адреса процессора и шину данных, таким же образом, как память. При адресации внутренней памяти шина данных находится в третьем состоянии, а управляющие сигналы в пассивном состоянии (высоком).

Взаимодействие c памятью и устройствами ввода/вывода на различных скоростях сопровождается сигналом READY. При связи с медленными устройствами, TMS320C2x ждет, пока устройство не завершит свою работу и просигнализирует процессору об этом через линию READY, после чего процессор продолжит работу.

Центральное арифметико-логическое устройство

Центральное арифметическо-логическое устройство (CALU) содержит 16-разрядный масштабирующий регистр сдвига, 16 x 16 параллельный умножитель, 32-разрядное арифметическо-логическое устройство (ALU), 32-разрядный аккумулятор и несколько дополнительных сдвиговых регистров, расположенных как на выходе из умножителя, так и на выходе из аккумулятора.

Любая операция ALU выполняется в следующей последовательности:

- данные захватываются из RAM на шину данных,

- данные проходят через масштабирующий сдвиговый регистр и через ALU, в котором выполняются арифметические операции,

- результат передается в аккумулятор.

Один вход в ALU всегда соединен с выходом аккумулятора, а второй может получать информацию либо из регистра произведения (PR) умножителя, либо загружаться из памяти через масштабирующий сдвиговый регистр.

Конвейерные операции

Конвейер команд состоит из последовательности операций обращения ко внешней шине, которые возникают в течении выполнения команд. Конвейер "предвыборка-декодирование-выполнение" обычно незаметен для пользователя, за исключением некоторых случаев, когда конвейер должен быть прерван (например, при ветвлении). Во время работы конвейера предвыборка, декодирование и выполнение команд независимы друг от друга. Это позволяет командам перекрываться. Так в течении одного цикла две или три команды могут быть активны, каждая на разных этапах работы. Поэтому получается двухуровневый конвейер для TMS32020 и трехуровневый для TMS320C25.

Количество уровней конвейера не всегда влияет на скорость выполнения команд. Большинство команд выполняется за одно и то же количество циклов вне зависимости от того, из какой памяти выбираются команды: внешней, внутренней RAM или внутренней ROM.

Добавочные аппаратные средства, имеющиеся на процессоре TMS320C25, позволяют расширить количество уровней конвейера до трех, что повышает производительность процессора. К этим средствам относятся счетчик предзахватов (PFC), 16-разрядный стек микровызовов (MCS), регистр команд (IR), и регистр очереди команд (QIR).

При трехуровневом конвейере PFC содержит адрес следующей команды, которая должна быть предзахвачена. Как только предзахват осуществлен, команда загружается в IR. Если же IR хранит команду, которая еще не выполнена, то предзахваченная команда помещается в QIR. После этого PFC увеличивается на 1. Как только текущая команда будет выполнена, команда из QIR будет перегружена в IR, для дальнейшего исполнения.

Счетчик команд (PC) содержит адрес команды, которая должна быть выполнена следующей, и не используется для операций захвата.

Но обычно PC используется в качестве указателя на текущую позицию в программе. Содержимое PC увеличивается после каждой выполненной команды. Когда возникает прерывание или вызов подпрограммы, содержимое PC помещается в стек, чтобы в дальнейшем можно было выполнить возврат в нужное место программы.

Циклы предзахвата, декодирования и выполнения конвейера независимы друг от друга, это позволяет перекрываться исполняемым командам во времени. В течении любого цикла три команды могут быть одновременно активны, каждая на разных стадиях завершения.

Бесплатная накрутка подписчиков в инстаграме без усилий Как накручивают подписчиков в инстаграме

Бесплатная накрутка подписчиков в инстаграме без усилий Как накручивают подписчиков в инстаграме Как отправить видео другу в одноклассниках через сообщение Как вставить файл в ок

Как отправить видео другу в одноклассниках через сообщение Как вставить файл в ок Что делать если "поле объекта не обнаружено" Поле объекта не обнаружено наименование полное

Что делать если "поле объекта не обнаружено" Поле объекта не обнаружено наименование полное Установить прошивку CyanogenMod с помощью инсталлятора CyanogenMod Влияние на гарантию

Установить прошивку CyanogenMod с помощью инсталлятора CyanogenMod Влияние на гарантию Добавляем произвольный телефон в личном кабинете оператора мобильной связи Киевстар (Украина)

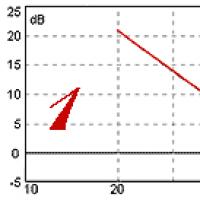

Добавляем произвольный телефон в личном кабинете оператора мобильной связи Киевстар (Украина) Что такое крутизна 12 дб окт

Что такое крутизна 12 дб окт Роуминг данных за границей

Роуминг данных за границей