Memoria asociativa. El desarrollo de la memoria asociativa. Memoria asociativa Otras aplicaciones AP incluyen

Una memoria de acceso aleatorio contiene típicamente una pluralidad de elementos de memoria idénticos que forman una matriz de memoria (SM). La matriz se divide en celdas individuales; cada uno de ellos está diseñado para almacenar un código binario, cuyo número de bits está determinado por el ancho de la muestra de memoria (en particular, puede ser una, la mitad o varias palabras de máquina). La forma en que se organiza la memoria depende de los métodos para colocar y recuperar información en la matriz de almacenamiento. Sobre esta base, distinga entre memoria de dirección, asociativa y de pila (almacenamiento).

Dirección de memoria. En la memoria direccionable, la ubicación y recuperación de información en el ZM se basa en el uso de la dirección para almacenar una palabra (números, comandos, etc.). La dirección es el número de la celda 3M en la que se coloca esta palabra.

Al escribir (o leer) una palabra en el ZM, el comando que inicia esta operación debe indicar la dirección (número de celda) en la que se realiza la escritura (lectura).

Una estructura típica de memoria de direcciones, contiene una matriz de memoria de celdas de N bits y su estructura de hardware, que incluye un registro de direcciones. RgA teniendo k (k»Log N) dígitos, registro de información RgI, bloque de selección de dirección BAS, bloque de lectura de amplificadores AUTOBÚS, bloque de amplificadores-modeladores de bits de señales de grabación BUZ y unidad de control de memoria BUP.

Por código de dirección en RgA BAV genera señales en la celda de memoria correspondiente que permiten leer o escribir una palabra en la celda.

El ciclo de acceso a la memoria se inicia con la llegada a BUP fuera de la señal Apelación... La parte general del ciclo de tratamiento incluye la admisión a RgA desde el bus de direcciones SHA direcciones de apelación y recepción en BUP y decodificación de la señal de control Operación indicando el tipo de operación solicitada (lectura o escritura).

Además, al leer BAS descifra la dirección, envía las señales de lectura a la celda ZM especificada por la dirección, mientras que el código de la palabra escrita en la celda es leído por los amplificadores de lectura ACC y transmitido a RgI... La operación de lectura termina con la salida de una palabra de RgI al bus de datos de salida Shivykh.

Al grabar, además de realizar la parte general anterior del ciclo de acceso, la palabra grabada se recibe desde el bus de información de entrada SHIVh y RgI... Luego al seleccionado BAS la celda se escribe una palabra de RgI.

Bloque de control BUP genera las secuencias necesarias de señales de control que inician el funcionamiento de los nodos de memoria individuales.

Memoria asociativa. En memoria de este tipo, la búsqueda de la información necesaria no se realiza por la dirección, sino por su contenido (por la característica asociativa). En este caso, una búsqueda por una característica asociativa (o secuencialmente por bits individuales de esta característica) ocurre en paralelo en el tiempo para todas las celdas de la matriz de almacenamiento. En muchos casos, la búsqueda asociativa puede simplificar y acelerar significativamente el procesamiento de datos. Esto se logra debido a que en este tipo de memoria, la operación de lectura de información se combina con la ejecución de una serie de operaciones lógicas.

Una estructura típica de memoria asociativa se muestra en la Fig. 4.3. La matriz de almacenamiento contiene celdas de N (n + 1) bits. Para indicar que la celda está ocupada, se usa el bit de servicio n-ésimo (0 - la celda está libre, 1 - se escribe una palabra en la celda).

Memoria asociativa

Memoria asociativa(AP) o Almacenamiento asociativo(CAM) es un tipo especial de memoria de máquina que se utiliza en aplicaciones de búsqueda muy rápidas. También conocido como memoria direccionable por contenido, almacenamiento asociativo, memoria direccionable por contenido o matriz asociativa aunque el último término se usa más comúnmente en programación para referirse a una estructura de datos. (Hannum et al., 2004)

Matriz asociativa de hardware

A diferencia de la memoria de máquina convencional (memoria de acceso aleatorio o RAM), en la que el usuario establece la dirección de la memoria y la RAM devuelve la palabra de datos almacenada en esta dirección, el UA está diseñado de tal manera que el usuario establece la palabra de datos y la UA lo busca en toda la memoria para saber si está almacenado en alguna parte. Si se encuentra una palabra de datos, el UA devuelve una lista de una o más direcciones de almacenamiento donde se encontró la palabra (y, en algunas arquitecturas, también devuelve la propia palabra de datos u otros datos relacionados). Por lo tanto, AP es una implementación de hardware de lo que en términos de programación se llamaría una matriz asociativa.

Estándares de la industria para memoria direccionable por contenido

La definición de la interfaz principal para la UA y otros elementos de búsqueda de red (NSE) se especificó en el Acuerdo de interoperabilidad llamado Interfaz Look-Aside ( LA-1 y LA-1B) que fue desarrollado por el Networking Forum, que luego se fusionó con el Optical Internetworking Forum (OIF). Numerosos dispositivos han sido fabricados por Integrated Device Technology, Cypress Semiconductor, IBM, Netlogic Micro Systems y otros bajo estos acuerdos de LA. El 11 de diciembre de 2007, la OIF emitió un Acuerdo de Interfaz Serial Lookaside. SLA).

Implementación en semiconductores

Debido a que el AP está diseñado para buscar toda la memoria en una sola operación, es mucho más rápido que buscar en la RAM en prácticamente todas las aplicaciones de búsqueda. Sin embargo, también existe una desventaja en el mayor costo del AP. A diferencia de un chip de RAM, que tiene un almacenamiento simple, cada bit individual de memoria en un AP completamente paralelo debe tener su propio circuito de comparación adjunto para encontrar una coincidencia entre el bit almacenado y el bit de entrada. Además, las salidas de comparación de cada celda en la palabra de datos deben combinarse para dar como resultado un resultado completo de comparación de palabras de datos. Los circuitos adicionales aumentan el tamaño físico del chip AP, lo que aumenta el costo de fabricación. Los circuitos adicionales también aumentan la disipación de energía, ya que todos los circuitos de comparación están activos en cada ciclo de reloj. Como consecuencia, AP solo se usa en aplicaciones especializadas donde la velocidad de búsqueda no se puede lograr usando otros métodos menos costosos.

Implementaciones alternativas

Para lograr un equilibrio diferente entre la velocidad, el tamaño de la memoria y el costo, algunas implementaciones emulan la funcionalidad de AP mediante el uso de algoritmos de hash estándar o de búsqueda de árbol implementados por hardware, y también utilizan trucos de hardware como la replicación y la canalización para acelerar la operación eficiente. Estos diseños se utilizan a menudo en enrutadores.

Memoria asociativa ternaria

La UA binaria es el tipo más simple de memoria asociativa que usa palabras de búsqueda de datos, que constan completamente de unos y ceros. El UA ternario agrega un tercer valor de comparación "X" o "no importante" para uno o más bits en la palabra de datos almacenada, agregando así más flexibilidad a la búsqueda. Por ejemplo, un AU ternario podría almacenar la palabra "10XX0", que coincidiría con cualquiera de las cuatro palabras de búsqueda "10000", "10010", "10100" o "10110". Agregar flexibilidad a la búsqueda se produce a expensas del costo AA binario, ya que la ubicación de la memoria interna ahora debe codificar tres estados posibles en lugar de dos. Este estado adicional generalmente se logra agregando un bit de máscara de gravedad (importante / no importante) a cada ubicación de memoria.

La memoria asociativa holográfica proporciona un modelo matemático para la memoria asociativa integrada del bit "no importante" utilizando una representación de valores complejos.

Ejemplos de aplicación

La memoria direccionable por contenido se utiliza a menudo en dispositivos de redes informáticas. Por ejemplo, cuando un conmutador de red recibe una trama de datos en uno de sus puertos, actualiza una tabla interna con el origen de la dirección MAC de la trama y el puerto en el que se recibió. Luego, busca la dirección MAC de destino en la tabla para determinar a qué puerto se debe enviar la trama y la envía a ese puerto. La tabla de direcciones MAC generalmente se implementa en un AP binario, por lo que el puerto de destino se puede encontrar muy rápidamente, lo que reduce la latencia del conmutador.

Los AP ternarios se utilizan a menudo en enrutadores de red en los que cada dirección tiene dos partes: (1) la dirección de red, que puede cambiar de tamaño según la configuración de la subred, y (2) la dirección del host, que ocupa los bits restantes. Cada subred tiene una máscara de red que determina qué bits son la dirección de red y qué bits son la dirección del host. El enrutamiento se realiza comprobando la tabla de enrutamiento que mantiene el enrutador. Contiene todas las direcciones de red de destino conocidas, su máscara de red asociada y la información que necesitan los paquetes enrutados a ese destino. Un enrutador, implementado sin el AP, compara la dirección de destino del paquete a dividir con cada entrada en la tabla de enrutamiento, realizando un AND lógico con la máscara de red y comparando los resultados con la dirección de red. Si son iguales, se utiliza la información de dirección correspondiente para enviar el paquete. El uso de un UA ternario para la tabla de enrutamiento hace que el proceso de búsqueda sea muy eficiente. Las direcciones se almacenan utilizando el bit "no importante" en la parte de la dirección del host, por lo que al buscar la dirección de destino en el UA se recupera inmediatamente la entrada correcta en la tabla de enrutamiento; Ambas operaciones, enmascaramiento y comparación, son realizadas en hardware por el AP.

Otras aplicaciones AP incluyen

- Administradores de caché de CPU y búferes de traducción asociativos (TLB)

Bibliografía

- Kohonen T. Dispositivos de almacenamiento asociativo. M.: Mir, 1982.- 384 p.

En inglés

- Anargyros Krikelis, Charles C. Weems (editores) (1997) Procesadores y procesadores asociativos, IEEE Computer Science Press. ISBN 0-8186-7661-2

- Hannum y col. (2004) Sistema y método para restablecer e inicializar una matriz totalmente asociativa a un estado conocido en el momento del encendido o mediante un estado específico de la máquina... NOSOTROS. Patente 6.823.434.

Enlaces

Fundación Wikimedia. 2010.

Vea qué es "Memoria asociativa" en otros diccionarios:

En informática, memoria sin direcciones, en la que se busca información por su contenido (característica asociativa). Ver también: Memoria de computadora Software de aplicación Vocabulario financiero Finam ... Vocabulario financiero

memoria asociativa- Memoria, en la que el direccionamiento no está determinado por la ubicación del objeto, sino por su contenido. Para encontrar la dirección, se analiza el objeto y su nombre (para ciertas palabras) coincide con otras direcciones. Usando memoria asociativa ... ... Guía del traductor técnico

memoria asociativa- memoria asociativa; memoria asociativa Un dispositivo de almacenamiento en el que el lugar de acceso está determinado por el contenido de la información almacenada ... Diccionario explicativo terminológico politécnico

memoria asociativa- asociatyvioji atmintis statusas T sritis automatika atitikmenys: angl. memoria asociativa vok. assoziativer Speicher, m; Durchsuchspeicher, m rus. memoria asociativa, f pranc. memoria asociativa, f… Automatikos terminų žodynas

MEMORIA ASOCIATIVA- Ver memoria, asociativo ... Diccionario explicativo de psicología

Este artículo debería estar wikificado. Rellénelo de acuerdo con las reglas de formato del artículo. La memoria humana es asociativa, es decir, alguna memoria puede generar un área grande asociada a ella. Un tema nos recuerda ... Wikipedia

Debido a la propiedad de la localidad, la mayoría de los programas acceden a una pequeña cantidad de páginas durante algún tiempo, por lo que solo se usa activamente una pequeña parte de la tabla de páginas.

Una solución natural al problema de la aceleración es equipar la computadora con un dispositivo de hardware para mapear páginas virtuales con páginas físicas sin acceder a la tabla de páginas, es decir, tener una memoria caché pequeña y rápida que almacena la parte de la tabla de páginas que está actualmente necesario. Este dispositivo se llama memoria asociativa, a veces también se utiliza el término búfer de traducción automática (TLB).

Una entrada de mesa en memoria asociativa(una entrada) contiene información sobre una página virtual: sus atributos y el marco en el que se encuentra. Estos campos corresponden exactamente a los campos de la tabla de páginas.

Como memoria asociativa contiene solo algunas de las entradas de la tabla de páginas, cada entrada de TLB debe incluir un campo numerado pagina virtual... La memoria se llama asociativa, porque compara simultáneamente el número de los pagina virtual con el campo correspondiente en todas las filas de esta pequeña tabla. Por tanto, este tipo de memoria es bastante caro. En línea, campo pagina virtual que coincide con el valor deseado, se encuentra el número de marco de página. Entradas típicas de TLB de 8 a 4096. Aumento del número de entradas en memoria asociativa debe hacerse teniendo en cuenta factores como el tamaño de la memoria caché principal y el número de accesos a la memoria por instrucción.

Considere el funcionamiento del administrador de memoria en presencia memoria asociativa.

Primera información de visualización pagina virtual en lo físico se busca en memoria asociativa... Si se encuentra la entrada requerida, todo está bien, excepto en los casos de violación de privilegios cuando se rechaza una solicitud de memoria.

Si la entrada deseada en memoria asociativa está ausente, la visualización se realiza a través de la tabla de páginas. Una de las entradas en memoria asociativa registro encontrado en la tabla de páginas. Aquí nos enfrentamos a un problema de reemplazo, que es tradicional para cualquier caché (es decir, cuál de las entradas en el caché debe cambiarse). Diseño memoria asociativa deben organizar los registros de tal manera que se pueda tomar una decisión sobre cuál de los registros antiguos debe eliminarse cuando se hagan nuevos.

Número de búsquedas exitosas de número de página en memoria asociativa en relación con el número total de búsquedas se denomina ratio de aciertos (coincidencia) (proporción, ratio). El término "porcentaje de aciertos de caché" también se utiliza a veces. Por lo tanto, la proporción de aciertos es la parte de los enlaces que se pueden crear utilizando memoria asociativa... Acceder a las mismas páginas aumenta la tasa de aciertos. Cuanto mayor sea la tasa de aciertos, menor será el tiempo medio de acceso a los datos en la RAM.

Suponga, por ejemplo, que se necesitan 100 ns para determinar la dirección en caso de que una caché no pase por la tabla de páginas, y para determinar la dirección en el caso de un acierto de la caché memoria asociativa- 20 ns. Con una tasa de aciertos del 90%, el tiempo medio de determinación de la dirección es 0,9x20 + 0,1x100 = 28 ns.

El rendimiento bastante aceptable del sistema operativo moderno demuestra la eficiencia de uso memoria asociativa... Alta probabilidad de encontrar datos en memoria asociativa asociado a la presencia de estas propiedades objetivas: localidad espacial y temporal.

Es necesario prestar atención al siguiente hecho. Al cambiar el contexto de los procesos, es necesario asegurarse de que el nuevo proceso no "vea" en memoria asociativa información relacionada con el proceso anterior, como su limpieza. Entonces usando memoria asociativa aumenta el tiempo de cambio de contexto.

El considerado de dos niveles ( memoria asociativa+ tabla de páginas) el esquema de traducción de direcciones es un excelente ejemplo de una jerarquía de memoria basada en el principio de localidad, como se discutió en la introducción de la lección anterior.

Tabla de páginas invertidas

A pesar de la organización por niveles, almacenar varias tablas de páginas grandes sigue siendo un problema. Su importancia es especialmente relevante para las arquitecturas de 64 bits, donde el número de páginas virtuales es muy grande. Una solución es usar tabla de páginas invertidas(tabla de páginas invertidas). Este enfoque se utiliza en máquinas PowerPC, algunas estaciones de trabajo Hewlett-Packard, IBM RT, IBM AS / 400 y varias otras.

Esta tabla contiene una entrada para cada marco de página en la memoria física. Es fundamental que una tabla sea suficiente para todos los procesos. Por lo tanto, se requiere una parte fija de la memoria principal para almacenar la función de visualización, independientemente de la arquitectura de bits, el tamaño y el número de procesos.

A pesar de los ahorros en RAM, el uso de mesa invertida tiene una desventaja significativa: las entradas en él (como en memoria asociativa) no están ordenados en orden ascendente de números de páginas virtuales, lo que complica la traducción de la dirección. Una forma de resolver este problema es utilizar una tabla hash. direcciones virtuales... Además, parte dirección virtual que representa el número de página se asigna a una tabla hash mediante una función hash. Cada página de memoria física aquí corresponde a una entrada en la tabla hash y tabla de páginas invertidas. Direcciones virtuales que tienen el mismo valor hash se concatenan entre sí. Normalmente, la longitud de la cadena no supera los dos registros.

Tamaño de página

Los diseñadores de sistemas operativos para máquinas existentes rara vez tienen la capacidad de influir en el tamaño de la página. Sin embargo, para las computadoras de nueva creación, la decisión sobre el tamaño de página óptimo es relevante. Como era de esperar, no existe un tamaño único que sea el mejor. Más bien, hay un conjunto de factores que afectan el tamaño. Normalmente, el tamaño de la página es una potencia de dos de 2 9 a 2 14 bytes.

En los dispositivos de almacenamiento asociativo, la información se busca mediante una característica asociativa registrada en cada celda de memoria.

En una memoria de este tipo, la búsqueda de la información necesaria se realiza no por la dirección, sino por el contenido de la información en sí (es decir, por la característica asociativa). En este caso, la búsqueda por una característica asociativa ocurre en paralelo en el tiempo para todas las celdas de memoria. La búsqueda asociativa puede simplificar y acelerar significativamente el procesamiento de datos. Esto se logra debido al hecho de que en dicha memoria la operación de lectura de información se combina con la ejecución de una serie de operaciones lógicas. Por ejemplo, puede realizar operaciones como:

1) busque el número máximo o mínimo en la memoria;

2) buscar palabras encerradas en ciertos límites;

3) buscar las palabras más cercanas al rasgo asociativo, tanto del lado mayor como del menor, etc.

La memoria asociativa más simple suele realizar una sola operación sobre la selección de palabras, cuya característica coincide con la asociativa.

La matriz de almacenamiento (ZM) contiene N celdas, cada celda es n + 1 bit. Para indicar que la celda está ocupada, se utiliza el bit de servicio n-ésimo. Si en el n-ésimo bit hay 0, entonces la celda está libre, si es 1, entonces está ocupada.

Se envía un atributo de n bits al registro de características asociativas RGП a través de la entrada SD, y el código de máscara de búsqueda se envía al registro de máscara RGM. En este caso, el n-ésimo bit del registro RGM se pone a 0. La búsqueda asociativa se realiza solo por aquellos bits de característica que corresponden a "1" en el registro de máscara, es decir, por los denominados bits RGM desenmascarados. . Por lo tanto, al especificar el código de máscara M, puede seleccionar arbitrariamente los bits de la función mediante los cuales se realiza la búsqueda.

Para palabras de ZM, en las que todos los dígitos coinciden con los bits desenmascarados de RGP, el circuito combinado KS 1 establece "1" en los bits correspondientes del registro de coincidencia RGC. Por lo tanto, si hubo una coincidencia del dígito de la j-ésima palabra con los bits no enmascarables del atributo, entonces "1" se escribirá en el j-ésimo bit del registro RGC, en caso contrario, "0". Escribir "1" en el j-ésimo bit del RGC significa que la j-ésima palabra corresponde a la característica, es decir, es la palabra que realmente se busca en ZM.

Se escribe una palabra en el registro de máscara, lo que permite una consulta para todos o solo algunos bits del atributo asociativo, el uso de una máscara le permite acortar o expandir el área de búsqueda.

La búsqueda de información se realiza en paralelo en todas las celdas comparando la solicitud con el atributo asociativo de cada celda.

El resultado de la búsqueda está formado por un circuito combinacional especial que genera señales que notifican sobre la ausencia de palabras que satisfacen las condiciones de búsqueda, sobre la presencia de una sola palabra, sobre la presencia de varias palabras con tal característica asociativa.

Después de la formación y procesamiento de las señales de advertencia, el circuito de control lee la información necesaria.

Al registrar información, primero se encuentra una celda libre. Para ello, se realiza una operación de búsqueda asociativa mediante una característica que tiene "0" en todos los bits, y "0" en el registro de máscara se escribe en todos los bits, excepto en el n-ésimo bit menos significativo.

Por lo tanto, se determinan aquellas celdas 3M para las cuales se escribe “0” en el n-ésimo dígito, lo que significa que la celda no está ocupada. La palabra del registro de información RGI se escribe en la celda libre con el número más bajo.

Al utilizar circuitos combinacionales adicionales en la memoria asociativa, puede realizar varias operaciones lógicas, determinando el número máximo o mínimo, el número de palabras que tienen el mismo atributo asociativo, etc. La figura 1 muestra la estructura de la memoria asociativa. Las celdas de memoria de la memoria asociativa deben ser elementos de memoria estática, en la memoria asociativa se accede a todas las celdas simultáneamente y no deben ser interrumpidas por ciclos de regeneración. La memoria asociativa es la más rápida, pero muy cara, ya que requiere la introducción de un esquema de comparación adicional que le permite realizar una búsqueda para cada celda de memoria. Por lo tanto, dicha memoria generalmente no se usa en su forma pura, y los dispositivos de memoria de alta velocidad como Cache generalmente se ejecutan como parcialmente asociativos.

En los microprocesadores, la memoria asociativa (memoria con recuperación de contenido) se usa como parte de la memoria caché para almacenar la porción de dirección de instrucciones y operandos del programa ejecutable. En este caso, no es necesario acceder a la RAM para el siguiente comando o el operando requerido, basta con poner la dirección necesaria en el registro del atributo asociativo y, si la información requerida está disponible en la memoria caché, se emitirá de inmediato. El acceso a la RAM será necesario solo si la información requerida no está en el caché. Debido a este uso de la caché, se reduce el número de llamadas a la RAM, y esto ahorra tiempo, ya que acceder a la caché requiere aproximadamente 10 veces menos tiempo que acceder a la RAM.

Organización de la memoria de pila

Si la escritura y la lectura se realizan a través del mismo registro, entonces dicho dispositivo se llama memoria de pila, y funciona según el principio de "primero en entrar, último en salir" (FILO-Primera entrada, última salida).

La memoria de pila, así como la memoria asociativa, no tiene direcciones, es una colección de celdas que forman una matriz unidimensional, en la que las celdas vecinas están conectadas entre sí mediante cadenas de transmisión de palabras de bits. Las palabras siempre se escriben en la celda cero superior. En este caso, todas las palabras escritas anteriormente se desplazan hacia abajo una celda. La lectura se realiza en el orden inverso al de la escritura.

La memoria de pila está muy extendida. Para implementarlo, una parte de la memoria de la pila se asigna en RAM mediante programas del sistema operativo. En la práctica, la memoria de pila se organiza a menudo utilizando una memoria de direcciones ordinaria.

Consideremos la organización de la memoria de pila como una memoria formada a partir de celdas de memoria interconectadas, en la que la información se desplaza hacia abajo cuando se escribe una nueva palabra en la pila (Fig. 2). El intercambio de información se lleva a cabo solo a través de la celda de memoria superior. Al leer palabras de la pila, la palabra puede eliminarse de la memoria de la pila o moverse por el anillo, según la organización de la pila. El modo de lectura (último en entrar, primero en salir) se denomina LIFO (último en entrar, primero en salir).

Figura 2 Organización de la memoria de pila.

La implementación de hardware de dicha memoria no siempre es aconsejable y, a menudo, la memoria de la pila se organiza en la memoria principal de la computadora mediante programación, lo que le permite cambiar el tamaño de la pila según la necesidad. Al organizar una pila, se asigna un registro de direcciones especial en la memoria principal: el "puntero de pila". El puntero de pila contiene la dirección de la última palabra introducida en la pila. Cuando se escribe una palabra en la pila, la dirección de la parte superior de la pila se reduce automáticamente; cuando se lee, se incrementa automáticamente. La memoria de pila se usa generalmente para guardar el estado del programa actual mientras se procesa una interrupción. Después de la ejecución del programa de interrupción, el estado de todos los registros que existían en el momento de la interrupción del programa se restaura en la secuencia inversa de la secuencia de escritura. También puede guardar datos del programa en la pila, esto es conveniente porque al acceder a la pila, no necesita especificar las direcciones de la celda de memoria en el programa, la recuperación de información de la pila también ocurre sin especificar la dirección.

Información general y clasificación de dispositivos de memoria.

Tema 2. Organización de la memoria informática.

Minisupercomputadora y superminicomputadora.

Pequeños y microordenadores.

Existe una gran cantidad de aplicaciones "pequeñas" relativamente hablando de las computadoras, como la automatización del control de producción de productos, el procesamiento de datos durante los experimentos, la recepción y procesamiento de datos de una línea de comunicación, el control de procesos tecnológicos, el control de máquinas herramienta y varios terminales digitales, pequeños problemas de ingeniería computacional ...

Actualmente, las pequeñas y microcomputadoras están integradas en varios dispositivos "inteligentes" (contadores eléctricos, hornos microondas, lavadoras, módems, sensores, etc.).

La clasificación carece de límites claros entre los tipos de computadoras considerados. Recientemente, se han comenzado a distinguir dos tipos intermedios.

Las superminicomputadoras incluyen computadoras de alto rendimiento que contienen uno o más procesadores débilmente acoplados combinados con una red troncal común (bus común). Es característico de una supermini computadora que la velocidad de sus operaciones aritméticas en números de punto flotante sea significativamente menor que la velocidad de operación, determinada por la mezcla de comandos correspondientes a consultas lógicas de información. Este tipo incluye la computadora de ajedrez IBM Deep Blue.

Las mini-supercomputadoras son computadoras multiprocesador simplificadas (en particular, debido a una palabra más corta), la mayoría de las veces con medios de procesamiento de vectores y tuberías, con una alta velocidad para realizar operaciones en números de punto flotante. Este tipo incluye equipos con arquitectura SMP (multiprocesador simétrico).

| Los dispositivos de almacenamiento se pueden clasificar de acuerdo con los siguientes criterios: · por el tipo de elementos de almacenamiento · por el propósito funcional · por el tipo de organización de la circulación · por la naturaleza de la lectura · por el método de almacenamiento · por el método de organización Por el tipo de elementos de almacenamiento Semiconductor Condensador magnético Optoelectrónico Holográfico Criogénico Por finalidad funcional RAM RAM VZU ROM EPROM | Por vía de organización del tratamiento Con búsqueda secuencial Con acceso directo Con acceso directo o Dirección Pila asociativa Almacén Por naturaleza de lectura Con destrucción de información Sin destrucción de información Por método de almacenamiento Estático Dinámico Por método de organización Una coordenada Dos coordenadas Tres coordenadas Dos -tres coordenadas |

Memoria Una computadora es un conjunto de dispositivos que se utilizan para almacenar, almacenar y emitir información. Los dispositivos individuales incluidos en este conjunto se denominan dispositivos de almacenamiento o recuerdos de un tipo u otro.

El rendimiento y las capacidades informáticas de una computadora están determinadas en gran medida por la composición y las características de su memoria. Como parte de una computadora, se utilizan simultáneamente varios tipos de dispositivos de memoria, que difieren en el principio de funcionamiento, las características y el propósito.

Las operaciones principales en la memoria son ingresar información en la memoria: grabación y recuperar información de la memoria - leyendo... Ambas operaciones se denominan acceso a la memoria.

Al acceder a la memoria, se lee o escribe una determinada unidad de datos, diferente para dispositivos de diferentes tipos. Una unidad de este tipo puede ser, por ejemplo, un byte, una palabra de máquina o un bloque de datos.

Las características más importantes de los dispositivos de memoria individuales (dispositivos de memoria) son la capacidad de memoria, la capacidad específica y la velocidad.

Capacidad de memoria está determinada por la cantidad máxima de datos que se pueden almacenar en él.

Capacidad especifica es la relación entre la capacidad de almacenamiento y su volumen físico.

Densidad de grabación es la relación entre la capacidad de almacenamiento y el área del transportador. Por ejemplo, los discos duros con una capacidad de hasta 10 GB tienen una densidad de grabación de 2 GB por metro cuadrado. pulgada.

Velocidad de memoria está determinado por la duración de la operación de acceso, es decir, el tiempo dedicado a buscar la unidad de información deseada en la memoria y leerla ( leer el tiempo de acceso), o el tiempo para buscar un lugar en la memoria destinado a almacenar una determinada unidad de información y escribirla en memoria (tiempo de acceso al grabar).

Duración del acceso a la memoria (tiempo del ciclo de la memoria) al leer

donde es el tiempo de acceso, que está determinado por el intervalo de tiempo entre el momento del inicio de la operación de acceso durante la lectura hasta el momento en que es posible acceder a esta unidad de información; - la duración del propio proceso físico de lectura, es decir, el proceso de detección y fijación de los estados de los correspondientes elementos de almacenamiento o áreas de la superficie del soporte de información.

En algunos dispositivos de memoria, la lectura de información va acompañada de su destrucción (borrado). En este caso, el ciclo de acceso debe contener la operación de restaurar (regenerar) la información leída en el mismo lugar de la memoria.

Duración del acceso (tiempo de ciclo) al grabar

donde es el tiempo de acceso durante la grabación, es decir, el tiempo desde el momento del inicio del acceso durante la grabación hasta el momento en que es posible acceder a los elementos de almacenamiento (o áreas de la superficie del medio), en el que la grabación está hecho; - tiempo de preparación dedicado a la inicialización de elementos de almacenamiento o áreas de la superficie del soporte de información para registrar una determinada unidad de información (por ejemplo, un byte o una palabra); - el momento de ingresar la información, es decir, cambiar el estado de los elementos de almacenamiento (secciones de la superficie del soporte). En la mayor parte

El valor se toma como la duración del ciclo de acceso a la memoria.

Dependiendo de las operaciones implementadas en la memoria, se distinguen los accesos: a) memoria con acceso aleatorio (los datos se pueden leer y escribir en la memoria); b) memoria solo para lectura de información ("permanente" o "unidireccional"). El registro de información en la memoria permanente se lleva a cabo en el proceso de su fabricación o ajuste.

Estos tipos de memoria corresponden a los términos RAM (memoria de acceso aleatorio) y ROM (memoria de solo lectura).

Según el método de organización del acceso, los dispositivos de memoria se distinguen por accesos directos (arbitrarios), directos (cíclicos) y secuenciales.

En la memoria desde directo (arbitrario) el acceso, el tiempo de acceso, y por tanto el ciclo de acceso, no dependen de la ubicación del área de memoria desde la que se realiza la lectura o en la que se escribe la información. En la mayoría de los casos, el acceso directo se realiza mediante dispositivos de almacenamiento electrónicos (semiconductores). En tales memorias, el ciclo de inversión suele ser de 70 nanosegundos o menos. El número de bits leídos o escritos en la memoria con acceso directo en paralelo en el tiempo para una operación de acceso se llama ancho de muestreo.

Los otros dos tipos de memoria utilizan procesos electromecánicos más lentos. En dispositivos memoria de acceso directo, que incluyen dispositivos de disco, debido a la rotación continua del soporte de información, la capacidad de acceder a una determinada sección del soporte para leer o escribir se repite cíclicamente. En dicha memoria, el tiempo de acceso suele ser de unas pocas fracciones de segundo a varias decenas de milisegundos.

En mente con acceso secuencial las secciones del soporte de información se escanean secuencialmente hasta que la sección deseada del soporte toma alguna posición inicial. Un ejemplo típico es un dispositivo de almacenamiento de cinta magnética, el llamado. serpentinas serpentina). El tiempo de acceso puede llegar a varios minutos en casos desfavorables de ubicación de la información.

Un buen ejemplo de unidad de cinta es el uso de un adaptador ARVID con una videograbadora VHS. La capacidad de esta unidad es de 4 GB / 180 min.

Las memorias también difieren en las funciones realizadas en la computadora, que dependen, en particular, de la ubicación de la memoria en la estructura de la computadora.

Los requisitos de velocidad y capacidad de memoria están en conflicto. Cuanto más rápido sea el rendimiento, más difícil será lograrlo y más caro será aumentar la capacidad de la memoria. El costo de la memoria es una parte significativa del costo total de una computadora. Por lo tanto, la memoria de la computadora se organiza en forma de una estructura jerárquica de dispositivos de memoria con diferente velocidad y capacidad. En general, una computadora contiene los siguientes tipos de memoria, en orden de velocidad decreciente y capacidad creciente.

La estructura jerárquica de la memoria le permite combinar de manera rentable el almacenamiento de grandes cantidades de información con un acceso rápido a la información durante el procesamiento.

Cuadro 2.1.

RAM o memoria principal(OP) se refiere a un dispositivo que sirve para almacenar información (datos de programa, resultados de procesamiento intermedio y final) que se utiliza directamente en el proceso de realizar operaciones en la unidad aritmética lógica (ALU) y la unidad de control (CU) del procesador.

En el proceso de procesamiento de la información, se lleva a cabo una estrecha interacción del procesador y el OP. Los comandos y operandos del programa se envían desde el OP al procesador, en el que se realizan las operaciones previstas por el comando, y desde el procesador al OP, los resultados del procesamiento intermedio y final se envían para su almacenamiento.

Las características del OP afectan directamente a los principales indicadores de la computadora y, en primer lugar, a la velocidad de su funcionamiento. Por el momento, la RAM tiene una capacidad de varios MB a varios GB y un ciclo de unos 60 ns o menos. Los dispositivos de memoria OP se fabrican en circuitos integrados con un alto grado de integración (memoria de semiconductores).

Recientemente, varias empresas han anunciado el inicio de la producción en serie de chips de memoria dinámica de 1 GB. El líder reconocido es Samsung. El producto más popular en la actualidad son los chips de 64 MB. En el próximo año, se espera un uso generalizado de chips de 128 MB y 256 MB.

En algunos casos, la velocidad del OP resulta insuficiente y la máquina debe incluir SOP (búfer o memoria caché de varios cientos o miles de kilobytes con un ciclo de varios nanosegundos. Estos SOP se ejecutan en chips de memoria estática). La velocidad de la caché debe corresponder a la velocidad de la aritmética - dispositivos lógicos y de control del procesador. La memoria superoperativa (búfer) se utiliza para el almacenamiento intermedio de secciones de programa y grupos de datos leídos por el procesador desde el OP, como células de trabajo del programa. , registros de índice, para almacenar información de servicio utilizada en el control del proceso computacional, enlace entre los dispositivos lógicos de alta velocidad del procesador y el OP más lento.

La memoria de alta velocidad con acceso aleatorio y acceso directo se utiliza como OP y SOP.

Por lo general, la capacidad de la RAM resulta insuficiente para almacenar todos los datos necesarios en una computadora. Por lo tanto, la computadora contiene varios dispositivos de almacenamiento con acceso directo en discos (la capacidad de un dispositivo de almacenamiento en discos HDD es de 1 a 30 GB) y varios dispositivos de almacenamiento con acceso secuencial en cintas magnéticas (la capacidad de un dispositivo de almacenamiento es de 4 a 35 GB). GB).

RAM junto con SOP y algunas otras memorias de procesador especializadas forman memoria interna Ordenador (fig. 4.1). Forma de cargadores electromecánicos memoria externa Ordenadores, por lo que ellos mismos se denominan dispositivos de almacenamiento externo(OVC).

Un dispositivo de almacenamiento de cualquier tipo consiste en una matriz de almacenamiento que almacena información y bloques que sirven para buscar en la matriz, escribir y leer (y en algunos casos, para regenerar) información.

Una memoria de acceso aleatorio contiene típicamente una pluralidad de elementos de memoria idénticos que forman una matriz de memoria (SM). La matriz se divide en celdas individuales; cada uno de ellos está diseñado para almacenar un código binario, cuyo número de bits está determinado por el ancho de la muestra de memoria (en particular, puede ser una, la mitad o varias palabras de máquina). La forma en que se organiza la memoria depende de los métodos para colocar y recuperar información en la matriz de almacenamiento. Sobre esta base, distinga entre memoria de dirección, asociativa y de pila (almacenamiento).

Dirección de memoria. En la memoria direccionable, la ubicación y recuperación de información en el ZM se basa en el uso de la dirección para almacenar una palabra (números, comandos, etc.). La dirección es el número de la celda 3M en la que se coloca esta palabra.

Al escribir (o leer) una palabra en el ZM, el comando que inicia esta operación debe indicar la dirección (número de celda) en la que se realiza la escritura (lectura).

Una estructura típica de memoria de direcciones, contiene una matriz de memoria de celdas de N bits y su estructura de hardware, que incluye un registro de direcciones. RgA teniendo k (k»Log N) dígitos, registro de información RgI, bloque de selección de dirección BAS, bloque de lectura de amplificadores AUTOBÚS, bloque de amplificadores-modeladores de bits de señales de grabación BUZ y unidad de control de memoria BUP.

Por código de dirección en RgA BAV genera señales en la celda de memoria correspondiente que permiten leer o escribir una palabra en la celda.

El ciclo de acceso a la memoria se inicia con la llegada a BUP fuera de la señal Apelación... La parte general del ciclo de tratamiento incluye la admisión a RgA desde el bus de direcciones SHA direcciones de apelación y recepción en BUP y decodificación de la señal de control Operación indicando el tipo de operación solicitada (lectura o escritura).

Además, al leer BAS descifra la dirección, envía las señales de lectura a la celda ZM especificada por la dirección, mientras que el código de la palabra escrita en la celda es leído por los amplificadores de lectura ACC y transmitido a RgI... La operación de lectura termina con la salida de una palabra de RgI al bus de datos de salida Shivykh.

Al grabar, además de realizar la parte general anterior del ciclo de acceso, la palabra grabada se recibe desde el bus de información de entrada SHIVh y RgI... Luego al seleccionado BAS la celda se escribe una palabra de RgI.

Bloque de control BUP genera las secuencias necesarias de señales de control que inician el funcionamiento de los nodos de memoria individuales.

Memoria asociativa. En memoria de este tipo, la búsqueda de la información necesaria no se realiza por la dirección, sino por su contenido (por la característica asociativa). En este caso, una búsqueda por una característica asociativa (o secuencialmente por bits individuales de esta característica) ocurre en paralelo en el tiempo para todas las celdas de la matriz de almacenamiento. En muchos casos, la búsqueda asociativa puede simplificar y acelerar significativamente el procesamiento de datos. Esto se logra debido a que en este tipo de memoria, la operación de lectura de información se combina con la ejecución de una serie de operaciones lógicas.

Una estructura típica de memoria asociativa se muestra en la Fig. 4.3. La matriz de almacenamiento contiene celdas de N (n + 1) bits. Para indicar que la celda está ocupada, se usa el bit de servicio n-ésimo (0 - la celda está libre, 1 - se escribe una palabra en la celda).

| Arroz. 2.2. Estructura de memoria asociativa |

En el bus de datos de entrada SHIVh al registro de atributos asociativos RgAP en los bits 0..n-1 se recibe una solicitud asociativa de n bits, y en el registro de máscara Rgm- código de máscara de búsqueda, con n-bit Rgm se establece en 0. La búsqueda asociativa se realiza solo para un conjunto de bits RgAP correspondiente a 1 en Rgm(pedazos desenmascarados RgAP). Para palabras en las que los dígitos de los dígitos coinciden con los dígitos sin máscara RgAP, circuito combinacional Kansas establece los bits correspondientes del registro de coincidencia en 1 PrSv y 0 al resto de dígitos. Entonces el valor j-a categoría en PrSv definido por la expresión

PrSv (j)=

donde RgAP[I], Rgm[I] y ZM[Ji] - valores I-a categoría, respectivamente RgAP, RgM y j-y celdas ZM.

Esquema combinacional para la formación del resultado del tratamiento asociativo. FS formas de la palabra formada en PrSv, señala a 0, a 1, a 2 correspondientes a los casos de ausencia de palabras en ZM que satisfacen la característica asociativa, y la presencia de una (o más) palabras de este tipo.

Dar forma al contenido PrSv y señala un 0, un 1, un 2 por contenido RgAP, RgM y ZM llamada operación de control de asociación... Esta operación es una parte integral de las operaciones de lectura y escritura, aunque también tiene un significado independiente.

Al leer, primero, la asociación es monitoreada por una característica asociativa en RgAP... Entonces, cuando un 0 = 1, la lectura se cancela debido a la falta de la información requerida, cuando un 1 = 1, se lee en RgI palabra encontrada, para un 2 = 1 en RgI se lee una palabra de la celda que tiene el número más pequeño entre las celdas marcadas con 1 en PrSv... Desde RgI la palabra leída se muestra en Shivykh.

Al escribir, primero se busca una celda libre. Para ello, la operación de control de la asociación se realiza cuando RgAP= 111 ... 10 y Rgm= 00 ... 01, mientras que las celdas libres están marcadas con 1 en PrSv... Se selecciona una celda vacía con el número más bajo para grabar. Registra la palabra recibida de SHIVh en RgI.

Usando la operación de control de la asociación, es posible, sin leer palabras de la memoria, determinar por el contenido PrSv cuántas palabras hay en la memoria que satisfacen una característica asociativa, por ejemplo, para implementar solicitudes como cuántos estudiantes en un grupo tienen una calificación excelente en una disciplina determinada. Cuando se utilizan los circuitos combinacionales apropiados en la memoria asociativa, se pueden realizar operaciones lógicas bastante complejas, como buscar un número mayor (menor), buscar palabras encerradas en ciertos límites, buscar el número máximo (mínimo), etc. Asociativo La memoria se utiliza, por ejemplo, en la distribución dinámica de hardware de OP.

Tenga en cuenta que la memoria asociativa requiere elementos de memoria que se puedan leer sin destruir la información registrada en ellos. Esto se debe al hecho de que la búsqueda asociativa se lee en todo el ZM para todos los bits desenmascarados y no hay ningún lugar para almacenar información destruida temporalmente por la lectura.

Pila de memoria, además de asociativo, no tiene dirección. Una memoria de pila puede verse como una colección de celdas que forman una matriz unidimensional, en la que las celdas adyacentes están conectadas entre sí mediante circuitos de transferencia de palabras de bits. Se escribe una nueva palabra en la celda superior (celda 0), mientras que todas las palabras escritas anteriormente (incluida la palabra que estaba en la celda 0) se desplazan hacia las celdas adyacentes con números mayores en 1. La lectura solo es posible desde la celda de memoria superior (cero), mientras que, si se realiza la lectura con borrado, todas las demás palabras de la memoria se desplazan hacia arriba, a las celdas vecinas con números grandes. En esta memoria, el orden de lectura de las palabras sigue la regla: último en primer servicio. Varios dispositivos de este tipo también permiten la operación de lectura simple de una palabra desde la celda cero (sin borrarla y desplazar la palabra en la memoria). A veces, la memoria de pila se suministra con un contador de pila Cuentas, mostrando el número de palabras memorizadas. Señal Cuentas= 0 corresponde a una pila vacía, Cuentas= norte- 1 - pila llena.

Por lo general, la memoria de pila se organiza mediante la memoria de direcciones. En este caso, el contador de pila suele estar ausente, ya que el puntero de pila puede determinar el número de palabras en la memoria. La memoria de pila se usa ampliamente cuando se procesan estructuras de datos anidadas, cuando se ejecutan interrupciones y comandos sin dirección.

Organización arquitectónica del procesador de la computadora.

El procesador ocupa un lugar central en la arquitectura de la computadora, controlando la interacción de todos los componentes principales que componen la computadora.Procesa directamente la información, y el control del programa de este proceso descifra y ejecuta los comandos del programa, organiza las llamadas a la memoria de acceso aleatorio (RAM ), inicia operaciones si es necesario entrada / salida y operación de dispositivos periféricos, percibe y procesa solicitudes provenientes tanto de dispositivos informáticos como del entorno externo (organización del sistema de interrupción). La ejecución de cada comando consiste en realizar operaciones más pequeñas, microinstrucciones que realizan ciertas acciones elementales. El conjunto de microinstrucciones está determinado por el sistema de comando y la estructura lógica de una computadora en particular. Por lo tanto, cada comando de computadora se implementa mediante un microprograma correspondiente almacenado en una memoria de solo lectura (ROM). En algunos equipos (principalmente especializados), todas o parte de las instrucciones se implementan en hardware, lo que permite aumentar su rendimiento debido a la pérdida de cierta parte de la flexibilidad del conjunto de instrucciones de la máquina. Tanto una como la segunda forma de implementar comandos de computadora tienen sus pros y sus contras.

El lenguaje de microprogramación está destinado a describir dispositivos digitales que operan a nivel de registro. Tiene medios simples y visuales para describir palabras de máquina, registros, buses y otros elementos básicos de una computadora. Teniendo en cuenta lo anterior, la jerarquía de lenguajes para describir un proceso computacional en una computadora se puede representar, en el caso general, en cuatro niveles: (1) Operación booleana (operación de LANs combinacionales) => (2) microinstrucción (operación de los nodos de la computadora) => (3) comando (operación de la computadora) => (4) operador de la HLU (descripción del algoritmo del problema que se resuelve). Para determinar el tiempo entre microinstrucciones, se establece una unidad de tiempo (ciclo) durante el cual se ejecuta la microinstrucción más larga. Por lo tanto, la ejecución de un comando de computadora mediante pulsos de sincronización generados por un dispositivo procesador especial: un generador de reloj, la frecuencia del reloj (medida en MHz) determina en gran medida la velocidad de la computadora. Naturalmente, para otras clases de computadoras, este indicador está asociado con el rendimiento, determinado por factores adicionales como.

Ancho de acceso a la memoria,

Tiempo de muestra,

Profundidad de bits,

La arquitectura del procesador y sus coprocesadores,

En la figura se muestra un diagrama ampliado del procesador central (CPU) de alguna computadora formal, que muestra solo sus bloques principales: registros de control (UR), unidad de control (CU), ROM, unidad aritmética lógica (ALU), memoria de registro (RP), memoria caché y unidad de interfaz (IB). Junto con lo anterior, la CPU contiene una serie de otros bloques (interrupciones, protección OP, supervisión y diagnóstico, etc.), cuya estructura y finalidad no se consideran aquí. La unidad CU genera una secuencia de señales de control que inician la ejecución de la secuencia correspondiente de microinstrucciones (ubicadas en ROM) que implementan el comando actual. Junto con esto, la unidad de control coordina el funcionamiento de todos los dispositivos informáticos enviando señales de control, intercambio de datos de la CPU<->OP, almacenamiento y procesamiento de información, interfaz con el usuario, pruebas y diagnósticos, etc. Por lo tanto, es aconsejable considerar la unidad de control como una unidad CPU separada; sin embargo, en la práctica, la mayoría de los circuitos de control se distribuyen por toda la computadora. Están conectados por una gran cantidad de líneas de control que transmiten señales para sincronizar el funcionamiento en todos los dispositivos informáticos y reciben señales sobre su estado. El bloque UR está destinado al almacenamiento temporal de información de control y contiene registros y contadores que participan junto con el UU en el control del proceso computacional. El comando actual, su contenido se actualiza a la dirección del siguiente comando), el registro de comando ( RK) contiene el comando que se está ejecutando (sus salidas están asociadas a circuitos de control que generan señales distribuidas en el tiempo, necesarias para ejecutar comandos)

El bloque RP contiene registros de memoria de alta velocidad (mayor rendimiento que OP) de pequeño tamaño, lo que permite aumentar la velocidad y las capacidades lógicas de la CPU. Estos registros se utilizan en instrucciones mediante direccionamiento de registro abreviado (solo se indican los números de registro) y se utilizan para almacenar operandos, resultados de operaciones, como registros base e índice, punteros de pila, etc. En algunas CPU, los registros base e índice son parte del Bloque UT, como regla general, el RP se realiza en forma de dispositivos de almacenamiento integrados semiconductores de alta velocidad

El bloque ALU se utiliza para realizar operaciones aritméticas y lógicas sobre los datos provenientes del OP y almacenados en el RP, y opera bajo el control de la CU. ALU realiza operaciones aritméticas en números binarios con puntos fijos y flotantes, en números decimales y procesa información simbólica en palabras de longitud fija y variable. Las operaciones lógicas se realizan en bits individuales, grupos de bits, bytes y sus secuencias. El tipo de operación realizada por la ALU está determinado por el comando actual del programa que funciona actualmente, más precisamente, la ALU se utiliza para realizar cualquier operación que le asigne la CU. En el caso general, la información procesada por la computadora consiste en palabras que contienen un número fijo de n bits (por ejemplo, n = 8, 16, 32, 64, 128 bits). En este caso, la ALU debe poder realizar operaciones sobre palabras de n bits, los operandos vienen del OP a los registros de la ALU, y el UU indica la operación que se debe realizar sobre ellos, el resultado de cada operación aritmético-lógica. se almacena en un registro sumador especial, que es el registro principal para operaciones aritmético-lógicas.

El sumador está conectado a circuitos de puerta para realizar las operaciones necesarias en su contenido y el contenido de otros registros. Algunas computadoras tienen varios sumadores, con más de 4, se asignan a un grupo especial de registros de propósito general (RON). Estructuralmente, la ALU se realiza en una o varias LSI / VLSI, mientras que la CPU puede tener una ALU de propósito universal o varias especializadas para ciertos tipos de operación. En el último caso, la complejidad estructural de la CPU aumenta, pero su rendimiento aumenta debido a la especialización y simplificación de los esquemas para calcular operaciones individuales. Este enfoque se usa ampliamente en computadoras y supercomputadoras modernas de propósito general para aumentar su productividad. A pesar de las diferentes clases de computadoras, sus ALU usan los principios generales de realizar operaciones aritmético-lógicas. Las diferencias se relacionan con las soluciones de circuitos de la organización ALU y los principios de implementación de la operación, que aseguran la aceleración de su implementación.

La unidad de interfaz (IB) asegura el intercambio de información entre la CPU y el OP y la protección de las secciones del OP contra el acceso no autorizado para el programa actual, así como la conexión de la CPU con dispositivos periféricos y otros dispositivos externos (VU ), que pueden ser otros procesadores y computadoras ... En particular, el IB contiene dos registros que proporcionan comunicación con el OP: el registro de dirección de memoria (RAP) y el registro de datos de memoria (RDP). El primer registro se utiliza para almacenar la dirección de la celda OP con la que se intercambian los datos, y el segundo contiene los datos de intercambio reales. La unidad de control y diagnóstico (MCU) está diseñada para detectar fallas y fallas de los nodos de la CPU, restaurar el funcionamiento del programa actual después de fallas y localizar fallas en caso de fallas.

Teniendo esto en cuenta, presentemos el esquema general de ejecución del programa por parte del procesador. La ejecución del programa ubicado en el OP comienza con el hecho de que se envía la dirección de su primer comando al CS, se envía el contenido del CS al ATM y se envía una señal de control de lectura al OP. Después de un tiempo (correspondiente al tiempo de acceso al OP), la palabra direccionada (en este caso, el primer comando del programa) se extrae del OP y se carga en el RDP, luego el contenido del RDP se envía al CAROLINA DEL SUR. En esta etapa, el comando está listo para decodificar su CU y ejecutarse. Si el comando contiene una operación a realizar por la ALU, entonces se deben obtener los operandos requeridos. Si el operando está en el OP (y también puede estar en el UR), debe seleccionarse de la memoria. Para ello, se envía la dirección del operando al RAP y comienza el ciclo de lectura, el operando seleccionado de la memoria en el RDP se puede transferir a la ALU. Habiendo seleccionado así uno o varios operandos, ALU puede realizar la operación requerida, almacenando su resultado en uno de los RON. Si el resultado de la operación necesita ser memorizado en el OP, se debe enviar al RDP, se envía al RAP la dirección de la celda donde se va a colocar el resultado y se inicia el ciclo de escritura. Mientras tanto, el contenido de la CK aumenta para indicar el siguiente comando que se ejecutará. Por lo tanto, tan pronto como se complete la ejecución del comando actual, la búsqueda para la ejecución del siguiente comando del programa puede comenzar inmediatamente.

Además de transferir datos entre el OP y la CPU, es necesario asegurar el intercambio de datos con la VU, que se realiza mediante comandos de máquina que controlan las E / S. El orden natural de ejecución de los programas puede verse alterado cuando se recibe una señal de interrupción. Una interrupción es una solicitud de servicio que es manejada por la CPU que ejecuta el programa de servicio de interrupción asociado (IPP). Dado que la interrupción y su procesamiento pueden cambiar el estado interno de la CPU, se almacena en el OP antes del inicio del EPP. La preservación del estado se logra enviando el contenido de RK, UR y alguna información de control al OP. Una vez finalizado el EPP, se restablece el estado de la CPU, lo que permite que continúe la ejecución del programa interrumpido.

Consejos sencillos sobre cómo probar la operatividad de un transformador con un multímetro

Consejos sencillos sobre cómo probar la operatividad de un transformador con un multímetro Reparación de sistemas de alimentación ininterrumpida Propuesta comercial para la reparación de un sistema de alimentación ininterrumpida

Reparación de sistemas de alimentación ininterrumpida Propuesta comercial para la reparación de un sistema de alimentación ininterrumpida Reparación de UPS hágalo usted mismo: consejo del asistente Reparación de fuentes de alimentación ininterrumpida de apc

Reparación de UPS hágalo usted mismo: consejo del asistente Reparación de fuentes de alimentación ininterrumpida de apc La reparación de un multímetro m 830b no muestra un ohmímetro

La reparación de un multímetro m 830b no muestra un ohmímetro Programas para dibujar circuitos eléctricos.

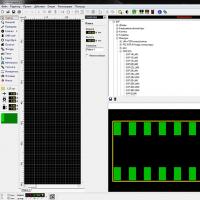

Programas para dibujar circuitos eléctricos. Dibujar tableros en Sprint-Layout correctamente desde los primeros pasos

Dibujar tableros en Sprint-Layout correctamente desde los primeros pasos ¿Qué programa puede abrir el archivo?

¿Qué programa puede abrir el archivo?