Programación mcs 51 en c. Microcontroladores MCS - 51. Diagrama de bloques, ALU, memoria de datos. Registros de funciones especiales

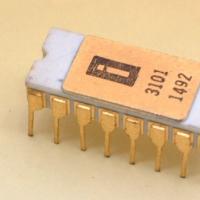

La arquitectura de la familia MCS-51 está predeterminada en gran medida por su propósito: construir compacto y barato dispositivos digitales. Todas las funciones de un microordenador se implementan utilizando un solo microcircuito. La familia MCS-51 incluye varios microcircuitos, desde los microcontroladores más simples hasta los más complejos. Los microcontroladores de la familia MCS-51 le permiten realizar tanto tareas de control para varios dispositivos como implementar nodos de circuitos analógicos individuales. Todos los microcircuitos de esta familia funcionan con el mismo sistema de mando MCS-51, la mayoría de ellos se realizan en los mismos casos con Pinout coincidente(numeración de patas para el cuerpo). Esto permite usar microcircuitos de diferentes compañías para el dispositivo desarrollado: Maxim, Atmel, NXP, etc. (catálogo..php? page = components_list & id = 39 "> ver búsqueda por parámetros) sin alterar el diagrama esquemático del dispositivo y el programa.

Figura 1. Diagrama de bloques del controlador I8751

El diagrama de bloques del controlador se muestra en la Figura 1 y consta de las siguientes unidades funcionales principales: unidad de control, unidad aritmética lógica, unidad de temporizador / contador, interfaz en serie y unidad de interrupción, contador de programa, memoria de datos y memoria de programa. El intercambio bidireccional se realiza mediante una autopista de datos interna de 8 bits.

Echemos un vistazo más de cerca al propósito de cada bloque. Casi todos los representantes de la familia MCS-51 se construyen de acuerdo con este esquema.... Varios microcircuitos de esta familia difieren solo en registros de propósito especial (incluido el número de puertos). Conjunto de comandos para todos los controladores de la familia MCS-51 contiene 111 comandos básicos con un formato de 1, 2 o 3 bytes y no cambia al pasar de un microcircuito a otro. Esto proporciona una excelente portabilidad de programas de un microcircuito a otro.

Unidad de control y sincronización

La unidad de Temporización y Control está diseñada para generar señales de sincronización y control que aseguren la coordinación del funcionamiento conjunto de las unidades OEVM en todos los modos permisibles de su operación. La unidad de control incluye:

- - un dispositivo para la formación de intervalos de tiempo,

- - lógica de E / S,

- - registro de comando,

- - registro de control del consumo de electricidad,

- - decodificador de comandos, lógica de control por computadora.

Dispositivo de configuración de franjas horarias está destinado a la formación y emisión de señales de sincronización internas de fases, relojes y ciclos. El número de ciclos de la máquina determina la duración de la ejecución de la instrucción. Casi todos los comandos OEVM se ejecutan en uno o dos ciclos de máquina, excepto los comandos de multiplicación y división, cuya duración es de cuatro ciclos de máquina. Designemos la frecuencia del oscilador maestro por F g. Entonces la duración del ciclo de la máquina es igual a 12 / F g o 12 períodos de la señal del oscilador maestro. La lógica de entrada y salida está diseñada para recibir y emitir señales que proporcionan intercambio de información con dispositivos externos a través de los puertos de entrada / salida P0-P3.

Registro de comando está diseñado para grabar y almacenar el código de operación de 8 bits del comando que se está ejecutando. El código de operación, con la ayuda del decodificador de comandos y la lógica de control de la computadora, se convierte en el microprograma de ejecución de comandos.

Registro de control de consumo (PCON) le permite detener el microcontrolador para reducir el consumo de energía y reducir el nivel de ruido del microcontrolador. Se puede lograr una mayor reducción del consumo de energía y reducción del ruido deteniendo el oscilador maestro del microcontrolador. Esto se puede lograr volteando un poco en el registro de control de consumo PCON. Para la variante n-MOS (serie 1816 o chips externos sin "c" en el medio), el Registro de control de consumo PCON contiene solo un bit que controla la velocidad en baudios del puerto serie SMOD y no hay bits de control de potencia.

Unidad aritmética lógica (ALU) es un dispositivo paralelo de ocho bits que realiza operaciones aritméticas y lógicas. ALU consta de:

- - registros acumuladores, registros de retención TMP1 y TMP2,

- - Constantes ROM,

- - sumador,

- - registro adicional (registro B),

- - batería (ACC),

- - registro de estado del programa (PSW).

Registrarse batería y tenencia de registros- registros de ocho bits destinados a recibir y almacenar operandos mientras duren las operaciones en ellos. Estos registros no son accesibles mediante programación.

Constantes ROM proporciona la generación de un código de corrección para la representación de datos binario-decimal, un código de máscara para operaciones de bits y un código constante.

Sumador paralelo de ocho bits es un circuito combinacional con acarreo secuencial, diseñado para realizar operaciones aritméticas de suma, resta y operaciones lógicas de suma, multiplicación, desiguales e idénticas.

Registro B- un registro de ocho bits utilizado durante las operaciones de multiplicación y división. Para otras instrucciones, puede verse como un registro superoperativo adicional.

Batería- un registro de ocho bits diseñado para recibir y almacenar el resultado obtenido al realizar operaciones aritmético-lógicas u operaciones de desplazamiento

Interfaz serie y unidad de interrupción (PIP) está destinado a la organización de entrada-salida de flujos secuenciales de información y la organización de un sistema para interrumpir programas. El bloque incluye:

- - búfer PIP,

- - lógica de control,

- - registro de control,

- - búfer del transmisor,

- - búfer del receptor,

- - transceptor de puerto serie,

- - registro de prioridad de interrupción,

- - registro de habilitación de interrupciones,

- - lógica para procesar banderas de interrupción y un circuito de generación de vectores.

Contador de programa está diseñado para generar la dirección actual de 16 bits de la memoria interna del programa y la dirección de 8/16 bits de la memoria externa del programa. El contador de instrucciones incluye un búfer de PC de 16 bits, un registro de PC y un circuito de incremento (aumentando el contenido en 1).

Memoria de datos (RAM) está destinado al almacenamiento temporal de la información utilizada en el proceso de ejecución del programa.

Puertos P0, P1, P2, P3 son puertos de entrada-salida cuasi-bidireccionales y están diseñados para asegurar el intercambio de información entre la computadora y los dispositivos externos, formando 32 líneas de entrada-salida.

Dispositivo temporizador Los modelos básicos de la familia tienen dos temporizadores / contadores programables de 16 bits (T / C0 y T / C1), que se pueden utilizar tanto como temporizadores como contadores de eventos externos.

Registro de estado del programa (PSW) destinado a almacenar información sobre el estado de la ALU durante la ejecución del programa.

Memoria de programa (EPROM) está diseñado para almacenar programas y es una memoria de solo lectura (ROM). Diferentes microcircuitos usan ROMs de máscara, borrables por radiación ultravioleta o DESTELLO ROM.

Registro de puntero de datos (DPTR) está destinado a almacenar una dirección de 16 bits de una memoria de datos externa o de una memoria de programa.

Puntero de pila (SP) es un registro de ocho bits diseñado para organizar un área especial de la memoria de datos (pila), en la que se puede almacenar temporalmente cualquier celda de memoria.

Los microcontroladores de la familia MCS-51 están construidos según la arquitectura de Harvard, en la que la memoria del programa y la memoria de datos están particionadas, tienen sus propios espacios de direcciones y formas de acceder a ellos.

Programa de memoria

El tamaño máximo de memoria es de 64 K bytes, de los cuales 4 K, 8 K, 16 K o 32 K bytes de memoria (Tabla 7.3.1) se encuentran en el chip, el resto está fuera de la matriz.

Con voltaje en el terminal EA =

V CC

se utilizan tanto la memoria interna como la externa, con EA = V CC = 0 - solo memoria externa.

La tabla 7.3.1 muestra programar direcciones de memoria para los casos indicados.

El área de memoria del programa inferior está asignada para iniciar la operación del microcontrolador (dirección de inicio 0000h después del reinicio) y para procesar interrupciones (las direcciones de interrupción se ubican con un intervalo de 8 bytes: 0003h, 000Bh, 0013h, etc.).

La memoria del programa es de solo lectura y cuando se accede a ella:

La memoria del programa es de solo lectura y cuando se accede a ella:

● para memoria externa programas, se genera la señal ¯PSEN y siempre se forma una dirección de 16 bits.

El byte bajo de la dirección se transmite a través del puerto P0 en la primera mitad del ciclo de la máquina y se fija en el borde de la luz estroboscópica ALE en el registro.

En la segunda mitad del ciclo, el puerto P0 se usa para ingresar un byte de datos desde la memoria externa al MC.

El byte de orden superior de la dirección se transmite a través del puerto P2 durante todo el tiempo de acceso a la memoria (Fig. 7.1.11);

● para memoria interna la señal de lectura no se genera y los ciclos de intercambio se utilizan en el bus interno del microcontrolador.

Memoria de datos

Memoria interna los datos se pueden dividir condicionalmente en tres bloques (Tabla 7.3.2).  La memoria interna siempre se direcciona mediante un byte, que solo se ocupa de 256 ubicaciones de memoria.

La memoria interna siempre se direcciona mediante un byte, que solo se ocupa de 256 ubicaciones de memoria.

Por tanto, como puede verse en la Tabla 7.3.2, para direccionar las celdas superiores de 8 bits de la RAM interna y los registros de funciones especiales SFR, ocupando el mismo espacio de direcciones, los comandos utilizan diferentes métodos de direccionamiento: indirecto y directo.

Características de la organización del área inferior de la RAM interna. se reflejan en la tabla 7.3.3.

Bajo 32 bytes de RAM interna con direcciones 00h.

1Fh se agrupan en cuatro bancos con ocho registros cada uno (R0.R7).

Siguientes 16 bytes de RAM con direcciones de 20 h.

2Fh representan un área de memoria de 8 × 16 = 128 bits, lo que permite acceder a cada bit individual.

Para seleccionar la dirección del registro bancario, se utiliza su nombre R0.

R7, para seleccionar un banco - bits RS0, RS1 del registro de palabra de estado PSW.

Direcciones de bit

Direcciones de bit se dan en la Tabla 7.3.3.

El direccionamiento se realiza directo camino.  En la Tabla 7.2.2 se da una lista de todos los registros de funciones especiales SFR con sus direcciones.

En la Tabla 7.2.2 se da una lista de todos los registros de funciones especiales SFR con sus direcciones.

Para mayor claridad, en la tabla 7.3.

4 espectáculos registrar mapa de direccionesSFR de los microcircuitos considerados de la familia MCS-51.

La dirección SFR se determina mediante una combinación de números de columna y línea en notación hexadecimal.

Por ejemplo, el registro CMOD tiene la dirección D9h.  Para registros SFR cuyas direcciones terminen en 0h u 8h (están en negrita), además de byte permitido bit a bit direccionamiento.

Para registros SFR cuyas direcciones terminen en 0h u 8h (están en negrita), además de byte permitido bit a bit direccionamiento.

En este caso, la dirección del bit que ocupa el bit N del registro se define como XXh + 0Nh, donde XXh es la dirección del registro SFR, N = 0,7.

Las direcciones de bit en esta área varían de 80H a FFH.

Por ejemplo, las direcciones de bit del acumulador ACC están en el rango E0h-E7h.

Memoria externa Los datos (hasta 64 KB) se crean mediante chips de memoria adicionales que están conectados al MC.

Para trabajar con memoria de datos externa, se utilizan comandos especiales, por lo que los espacios de direcciones de la memoria externa e interna no se superponen y, por lo tanto, ambos tipos de memoria de datos se pueden usar simultáneamente.

Para acceder a las celdas de la memoria de datos externa se utilizan (Figura 7.1.8):

● comandos con direccionamiento indirecto;

● señales para leer ¯RD y escribir ¯WR;

● puerto P0 para transmitir el byte menos significativo de la dirección y recibir / transmitir el byte de datos;

● Puerto P2 para transmitir el byte de orden superior de la dirección.

Métodos de abordaje.

El sistema de comando utiliza:

● direccionamiento directo, indirecto, de registro, de registro indirecto, directo e indexado (direccionamiento indirecto por la suma de los registros base e índice) operandos fuente;

● direccionamiento directo, de registro e indirecto de registro operandos de destino.

La combinación de estos métodos (direccionamiento) proporciona 21 modos de direccionamiento.

Esta y las siguientes tablas del sistema de comandos utilizan la siguiente notación:

Direccionamiento directo.

Con este método de direccionamiento, la ubicación del byte o bit de datos se determina mediante la dirección de 8 bits del segundo (y tercer) byte de comando.

El direccionamiento directo solo se utiliza para acceder a la memoria de datos interna (128 bytes inferiores de RAM) y registros de funciones especiales.

Registro de direcciones.

Este método de direccionamiento proporciona acceso a los datos almacenados en uno de los ocho registros R0.

R7 del banco actual de registros laborales.

También se puede utilizar para acceder a los registros A, B, AB (registro dual), registro de puntero DPTR y bandera de transporte C.

La dirección de estos registros está incrustada en el código de operación, lo que reduce el número de bytes de comando.

Direccionamiento indirecto de registros.

En este caso, la dirección de los datos se almacena en un registro de puntero, cuya ubicación está determinada por el código de operación.

Este método de direccionamiento se utiliza para acceder a la RAM externa y a la mitad superior de la RAM interna.

Los registros-punteros de direcciones de 8 bits pueden ser los registros R0, R1 del banco seleccionado de registros de trabajo o el puntero de pila SP; para el direccionamiento de 16 bits, solo se usa el registro de puntero de datos DPTR.

Direccionamiento directo.

Con este método de direccionamiento, los datos se indican directamente en el comando y se ubican en el segundo (o en el segundo y tercer) bytes del comando, es decir,

no se requiere direccionamiento de memoria.

Por ejemplo, mediante el comando MOV A, # 50, el número 50 se carga en el acumulador A.

Direccionamiento indexado.

Este método es un direccionamiento de registro indirecto, en el que la dirección del byte de datos se determina como la suma de los contenidos de los registros base (DPTR o PC) e índice (A).

Camino se utiliza solo para acceder a la memoria del programa y solo en modo lectura; facilita la visualización de tablas conectadas en la memoria del programa.

Estructura de mando.

La longitud de un comando es uno (49 comandos), dos (45 comandos) o tres (17 comandos) bytes.

El primer byte del comando siempre contiene el código de operación (OP), mientras que el segundo y tercer bytes son las direcciones de los operandos o valores de datos inmediatos.

Se pueden utilizar como operandos bits individuales, tétradas, bytes y palabras de doble byte.

Hay 13 tipos de comandos, que se muestran en la Tabla 7.3.5:

● A, PC, SP, DPTR, Rn (n = 0, 7) - acumulador, contador de instrucciones, puntero de pila, registro de puntero de datos y registro de banco actual;

● Rm (m = 0, 1) - registro del banco actual utilizado para el direccionamiento indirecto;

● directo: dirección de 8 bits del operando direccionado directamente;

● bit: la dirección del bit direccionado directamente;

● rel - dirección relativa de la transición;

● addr11, addr16: dirección de transición absoluta de 11 y 16 bits;

● # data8, # data16: datos directos (operandos) de 8 y 16 bits de longitud;

● A10, A9, A0: bits individuales de la dirección de 11 bits;

● (.): El contenido de la celda de memoria en la dirección especificada entre paréntesis;

● SB, MB: bytes altos y bajos del operando de 16 bits.

Información general sobre el sistema de mando.

El sistema de comando ofrece grandes posibilidades para procesar datos en forma de bits, cuadernos, bytes, palabras de doble byte, así como control en tiempo real.

El lenguaje ensamblador de macros ASM51 se utiliza para describir los comandos. La sintaxis de la mayoría de los comandos consiste en una designación nemotécnica (abreviatura) de la operación a realizar, seguida de los operandos.

Los operandos se utilizan para indicar diferentes métodos de direccionamiento y tipos de datos.

En particular, la abreviatura MOV tiene 18 instrucciones diferentes diseñadas para procesar tres tipos de datos (bits, bytes, direcciones) en diferentes espacios de direcciones.

El conjunto de comandos tiene 42 designaciones mnemotécnicas de 111 tipos de comandos para concretar 33 funciones MK.

De las 111 instrucciones, 64 se ejecutan en un ciclo de máquina, 45 en dos ciclos y solo dos instrucciones (MUL - multiplicación y DIV - división) se ejecutan en 4 ciclos. A una frecuencia de reloj de 12 MHz, la duración de un ciclo de máquina (12 ciclos de reloj) es de 1 μs. Por característica funcional Los equipos se pueden dividir en cinco grupos. A continuación se muestra una descripción de los comandos de cada grupo, presentados en forma de tablas. Para la compacidad de las tablas, destaquemos un grupo de comandos (Tabla 7.3.6), cuya ejecución influencias(marcado con +) sobre el estado de las banderas registro de palabra de estado PSW.

Comandos de transferencia de datos

Los comandos de transferencia se pueden dividir en subgrupos separados.

Comandos para transferir e intercambiar datos entre celdas de la memoria interna(Tabla 7.3.7).

Los comandos 1-16, que tienen el mnemónico MOV dest, src, son para reenvío byte o dos bytes (comando 16) de datos desde origen src hasta destino destino, mientras que:

● para indicar fuente(src) se utilizan cuatro métodos de direccionamiento: registro (comandos 2-4, 6, 8), directo (comandos 1, 7, 9, 11), indirecto (comandos 5, 10) y directo (comandos 12-16);

● para indicar receptor(dest)

Se utilizan tres métodos: registro (comandos 1, 3 ... 5, 9, 12, 14, 16), directo (comandos 2, 7, 8, 10, 13), indirecto (comandos 6, 11, 15).

Los equipos 17-20 proporcionan intercambio información entre dos celdas de la memoria interna de datos (o transferencia bidireccional).

Cuando se ejecutan los comandos XCH, se intercambian bytes y los comandos XCHD se intercambian con las tétradas inferiores de operandos de bytes.

Una de las celdas es siempre el acumulador A. Como otra celda, al intercambiar bytes, se usa uno de los registros Rn del banco actual, A es también una celda direccionable directa o indirectamente de la memoria interna; al intercambiar tétradas, solo una celda direccionable indirectamente de la memoria interna.

Dado que en todas las MCU la pila se encuentra en la RAM interna, este subgrupo incluye comandos(20, 21) acceso a la pila PUSH src, destino POP

Estos comandos usan solo el método de direccionamiento directo, escribiendo un byte en la pila o recuperándolo de la pila.

Debe tenerse en cuenta que en aquellas MCU que no tienen los 128 bytes superiores en RAM, aumentar la pila más allá de los 128 bytes conduce a la pérdida de datos.

Comandos de transferencia de datos entre la memoria de datos interna y externa(Tabla 7.3.8).

Estos comandos usan solo direccionamiento indirecto, mientras que la dirección de un byte se puede ubicar en P0 o R1 del banco de registros actual, y la dirección de dos bytes se puede ubicar en el registro de puntero de datos DPRT.

En cualquier acceso a la memoria externa, la batería A desempeña el papel de receptor o fuente de operandos en la memoria interna.  Instrucciones de transferencia de datos desde la memoria del programa(Tabla 7.3.9).

Instrucciones de transferencia de datos desde la memoria del programa(Tabla 7.3.9).

Estos comandos son para leer tablas de la memoria del programa.

La instrucción MOVC A, @ A + DPTR se utiliza para hacer referencia a una tabla con el número de entradas de 0 a 255.

El número de la entrada de la tabla requerida se carga en el acumulador y el registro DPTR se establece en el punto de inicio de la tabla. Una característica distintiva del otro comando es que el PC contador de programas se utiliza como puntero base y se accede a la tabla desde una subrutina. Primero, el número del punto de entrada requerido se carga en el acumulador, luego se llama a la subrutina con el comando MOVC A, @ A + PC. La tabla puede tener 255 entradas con números del 1 al 255, ya que 0 se utiliza para la dirección del comando RET de la salida de la subrutina.  Comandos de procesamiento de datos aritméticos. Todos los comandos aritméticos se ejecutan en enteros sin signo. Operaciones en dos operandos(Tabla 7.3.10). En operaciones adiciones AGREGAR, adición de transferencia ADDC y deducción de préstamo SUBB:

Comandos de procesamiento de datos aritméticos. Todos los comandos aritméticos se ejecutan en enteros sin signo. Operaciones en dos operandos(Tabla 7.3.10). En operaciones adiciones AGREGAR, adición de transferencia ADDC y deducción de préstamo SUBB:

● la fuente de un operando de 8 bits y el receptor del resultado es el acumulador;

● la fuente de otro operando es uno de los registros de trabajo Rn (n = 0-7) del banco actual, o directamente directo

o indirectamente @Rm (m = 0, 1) la ubicación de memoria direccionable de la RAM, o datos directos #data.

Operaciones multiplicación MUL y división Los DIV se realizan sobre el contenido de los registros A y B. Al multiplicar, los 8 bits más altos del resultado se escriben en el registro B, los 8 bits más bajos se escriben en el registro A.

Si el producto es mayor que 255, se establece el indicador de desbordamiento de OV; La bandera de acarreo C siempre se borra. La instrucción DIV divide el operando de 8 bits del acumulador A por el operando de 8 bits del registro B.

Durante la división, el cociente (bits más significativos) se escribe en el registro en A, el resto (bits menos significativos) en B. Se borran las banderas de acarreo C y OV de desbordamiento.

Un intento de dividir por 0 activa la bandera de desbordamiento de OV. La operación de división se usa más comúnmente para turnos y conversiones de base.

Cuando un número binario se divide por 2 N, se desplaza N bits hacia la izquierda.

Los bits adicionales se transfieren al registro B.

Operaciones en operandos de un solo byte(Tabla 7.3.11).

El comando DA se utiliza para realizar operaciones BCD. Los comandos INC, DEC permiten aumentar o disminuir respectivamente el contenido de la celda de memoria en uno.

Se aplican al contenido del acumulador A, uno de los registros de trabajo Rn, o una celda de memoria direccionada tanto directa como indirectamente.

La operación de incremento también se aplica al contenido del registro de puntero DPTR de 16 bits.

Comandos booleanos.

Operaciones dobles

(Tabla 7.3.12).

Los comandos AML, ORL, XRL permiten realizar tres operaciones lógicas de dos lugares en operandos de 8 bits: ANL - multiplicación lógica (AND), ORL - adición lógica (OR), XRL - OR exclusivo (XOR).

Las operaciones se realizan en bits individuales de los operandos. La fuente de uno de los operandos y al mismo tiempo el receptor del resultado es un acumulador (A) o una celda de memoria directamente direccionable (directa).

Para la fuente de otro operando, se utiliza un método de direccionamiento directo, indirecto o directo de registro.

Operaciones únicas

(Tabla 7.3.13).

El grupo también incluye una serie de operaciones individuales sobre el contenido del acumulador A: borrar (CLR), complemento lógico o inversión (CPL), desplazamientos cíclicos y cíclicos extendidos de 1 bit a la derecha (RL, RLC) y a la izquierda (RR, RRC), tétradas de intercambio o desplazamiento cíclico de un byte en 4 bits (SWAP), A también es una operación vacía (NOP), como resultado de lo cual el estado de todos los registros MC (excepto el contador del programa) permanece sin cambios.

Comandos de transferencia de control

Comandos de salto incondicionales

(Tabla 7.3.14).

Los comandos 1-3 difieren solo en el formato de la dirección de destino.

El comando LJMP (L - Long) realiza un salto incondicional "largo" a la dirección addr16 especificada, cargando el contador de la PC con el segundo y tercer bytes de comando.

El comando proporciona un salto a cualquier punto en el espacio de direcciones de 64 KB.

El comando AJMP (A - Absoluto) proporciona un salto "absoluto" a una dirección dentro de una página de 2K bytes, cuya dirección inicial se establece mediante los cinco bits más significativos del contador del programa de PC (al principio, el contenido de la PC es aumentado en 2).

El comando SJMP (S - Short) permite un salto incondicional "corto" a la dirección, que se calcula sumando el offset firmado rel en el segundo byte del comando con el contenido del contador de PC, previamente aumentado en 2.

La dirección de salto está dentro de -128 + 127 bytes en relación con la dirección del comando.

Para saltar a cualquier otro punto en el espacio de direcciones de 64 kilobytes, también se puede usar el comando 4 con una dirección indirecta @ A + DPTR.

En este caso, el contenido de A se interpreta como un entero sin signo.  Operación nula (NOP), como resultado de lo cual el estado de todos los registros del microprocesador (excepto el contador del programa) permanece sin cambios.

Operación nula (NOP), como resultado de lo cual el estado de todos los registros del microprocesador (excepto el contador del programa) permanece sin cambios.

Comandos de rama condicional

(Tabla 7.3.15).

Con la ayuda de los comandos JZ y JNZ, se realiza un salto si el contenido del acumulador es respectivamente igual o no igual a cero.

La dirección de salto se calcula agregando el desplazamiento de signo relativo rel al contenido del contador de comandos de la PC después de agregarle el número 2 (longitud del comando en bytes).

El contenido de la batería permanece sin cambios.

Los comandos no afectan a las banderas.  Los comandos CJNE (3-6) se utilizan para implementar un salto condicional basado en el resultado de comparar dos operandos de 8 bits, cuya ubicación se indica en los comandos.

Los comandos CJNE (3-6) se utilizan para implementar un salto condicional basado en el resultado de comparar dos operandos de 8 bits, cuya ubicación se indica en los comandos.

Si sus valores no son iguales, se realiza una ramificación.

La dirección de salto se calcula sumando el offset rel con el contenido del contador de PC, previamente aumentado en 3.

De lo contrario, se ejecuta el siguiente comando.

La columna Algoritmo muestra el efecto de los valores de los operandos de 8 bits comparados en la bandera de acarreo C.

Los comandos DJNZ (7) están diseñados para organizar ciclos de programa.

El registro Rn o la celda direccionable directa representa el contador de repetición del ciclo, y el desplazamiento rel (en el segundo y tercer bytes de comando) es la dirección relativa del salto al comienzo del ciclo.

Cuando se ejecutan los comandos, el contenido del contador se reduce en uno y se comprueba en cero.

Si el contenido del contador no es igual a cero, se realiza la transición al inicio del ciclo.

De lo contrario, se ejecuta el siguiente comando.

La dirección de salto se calcula agregando el desplazamiento al contenido del contador, previamente aumentado por la longitud del comando (en 2 o 3).

Las banderas de comando no se ven afectadas.

Comandos para llamar subrutinas y regresar de programas

(Tabla 7.3.16).

Los comandos de llamada larga LCALL y llamada absoluta ACALL llaman incondicionalmente a la subrutina ubicada en la dirección especificada.

La diferencia entre estas instrucciones y las instrucciones de salto incondicional discutidas anteriormente es que almacenan la dirección de retorno (el contenido del contador) en el programa principal de la pila.

El comando de retorno de la subrutina RET restaura el valor del contenido del contador del programa de la pila, y el comando RETI también habilita interrupciones del nivel de servicio.  El direccionamiento relativo se usa ampliamente en los comandos de transferencia de control, que admite módulos de programa reubicables.

El direccionamiento relativo se usa ampliamente en los comandos de transferencia de control, que admite módulos de programa reubicables.

Un rel de desplazamiento con signo de 8 bits actúa como una dirección relativa, lo que proporciona una bifurcación desde la posición actual del contador de PC en ambas direcciones en ± 127 bytes.

Para saltar a cualquier otro punto en el espacio de direcciones de 64K bytes, se puede usar la dirección directa addr16 o la dirección indirecta @ A + DPTR.

En el último caso, el contenido de A se interpreta como un entero sin signo.

Se introdujo una variante del direccionamiento directo corto addr11 dentro de una página actual de 2K bytes para compatibilidad con la arquitectura MK48.

Todos estos tipos de direccionamiento solo se pueden aplicar a la operación de sucursal, y para la operación de llamada solo se permiten los métodos de direccionamiento directo addr16 y addr11 interno.

En todas las operaciones condicionales, solo se puede utilizar el direccionamiento relativo.

Cuando el MK51 reconoce una solicitud de interrupción, genera una de las instrucciones LCALL addr16, que automáticamente asegura que la dirección de retorno se almacene en la pila.

Sin embargo, a diferencia de MK48, MK51 no tiene información de estado guardada automáticamente.

En este caso, la lógica de interrupción deja de responder a las solicitudes del nivel que se aceptó para el servicio.

Para bajar el nivel de interrupción se utiliza el comando de retorno de la interrupción RETI que, además de la operación equivalente a RET, incluye la operación de habilitación de la interrupción de este nivel.

Las operaciones JZ, JNZ también pertenecen a las operaciones condicionales estándar MK51.

Sin embargo, hay una nueva operación "Compare and Go" CJNE.

Para este comando, primero se compara el operando de acuerdo con las reglas de sustracción de enteros con una constante, y de acuerdo con el resultado de la comparación, se establece la bandera CY. Luego, en caso de una discrepancia con una constante, la ramificación es realizado. Al comparar un acumulador, registro o celda de memoria con una secuencia de constantes, obtenemos una forma conveniente de verificar coincidencias, por ejemplo, para identificar casos especiales.

De hecho, el comando CJNE es miembro del operador de lenguaje de alto nivel CASE.

El equipo de DJNZ se desarrolló aún más.

Ahora el programador como contador puede usar no solo uno de los registros de trabajo Rn, sino también cualquier celda de memoria DSEG.

Comandos de operaciones de bits.

El grupo consta de 12 comandos que le permiten realizar operaciones en uno o dos bits (reset, set, inversión de bit, A también lógico AND y OR), y 5 comandos diseñados para implementar saltos condicionales (Tabla 7.3.17).

Las instrucciones proporcionan direccionamiento directo de 128 bits ubicados en dieciséis celdas de la RAM interna con direcciones 20h.

2Fh (Tabla 7.3.3) y 128 bits ubicados en registros de propósito especial cuyas direcciones son múltiplos de ocho (resaltados en la Tabla 7.3.4 en negrita).

Cuando se realizan operaciones en dos operandos de un bit, el flip-flop del registro PSW se utiliza como acumulador lógico, que almacena la bandera de acarreo C (cuadro 7.1.2).

Las instrucciones MOV (1,2) realizan envío bits de una celda de bits directamente direccionable de la RAM interna al flip-flop C o viceversa.

Comandos CRL (3, 4), SETB (5, 6) respectivamente vertedero a cero o establecer a una bandera de acarreo C o al bit especificado.

Con la ayuda de los comandos CPL, ANL, ORL (7-12), se realizan las operaciones lógicas de inversión, suma y multiplicación.

El grupo también incluye comandos (13-17) para implementar operaciones de bifurcación condicionales con un desplazamiento relativo de 8 bits rel.

Las transiciones se pueden implementar tanto cuando se establece un bit o un indicador de acarreo (comandos 13, 16) como cuando se borra (comandos 14, 17).

El comando JBC, además de moverse a la dirección calculada, cuando se cumple la condición (bit) = 1, restablece este bit a cero.

Al ejecutar comandos de bifurcación condicional, la dirección de salto se calcula después de sumar los números 3 o 2 al contenido del contador (reflejando el número de bytes en el comando).

- Comandos aritméticos;

- Comandos lógicos;

- Comandos de transferencia de datos;

- Comandos del procesador de bits;

- Comandos de transferencia de ramificación y control.

- Registro de direcciones

- Direccionamiento directo

- Direccionamiento de registro indirecto

- Direccionamiento directo

- Direccionamiento indirecto de registros por la suma de los registros base e índice

| Designación, símbolo | Cita |

| A | Batería |

| Rn | Registros del banco de registro actualmente seleccionado |

| r | El número del registro cargado especificado en el comando |

| directo | Dirección de celda de datos interna de 8 bits direccionable directamente, que puede ser una celda de RAM de datos interna (0-127) o SFR (128-255) |

| @Rr | Célula de 8 bits direccionable indirectamente de la RAM de datos interna |

| datos8 | Datos directos de 8 bits que van al CPC |

| dataH | Bits más significativos (15-8) de datos directos de 16 bits |

| dataL | Los bits menos significativos (7-0) de datos directos de 16 bits |

| addr11 | Dirección de destino de 11 bits |

| DIRECCIÓN | Los bits menos significativos de la dirección de destino |

| disp8 | Desplazamiento de bytes de 8 bits con signo m |

| poco | Bit direccionable directo cuya dirección contiene el CPC ubicado en la RAM de datos interna o SFR |

| a15, a14 ... a0 | Bits de dirección de destino |

| (NS) | Contenido del elemento X |

| ((NS)) | Contenido en la dirección almacenada en el elemento X |

| (X) [M] | Descarga M del elemento X |

| + - * / Y O XOR / X | Operaciones: suma, resta, multiplicación, división, multiplicación lógica (operación Y), suma lógica (operación O), suma módulo 2 (O exclusivo), inversión del elemento X |

Los mnemónicos de función están asociados de forma única con combinaciones específicas de métodos de direccionamiento y tipos de datos. Un total de 111 combinaciones de este tipo son posibles en el sistema de mando. La tabla proporciona una lista de comandos, ordenados alfabéticamente.

| Mnemotécnica | Función | Banderas |

| Comando ACALL | Llamada de subrutina absoluta | |

| AÑADIR Equipo A,<байт-источник> | Adición | AC, C, OV |

| Equipo A de ADDC,<байт-источник> | Llevar plegado | AC, C, OV |

| Equipo AJMP | Transición absoluta | |

| Equipo ANL<байт-назначения>, <байт-источникa> | "Y" lógico | |

| Equipo ANL C,<байт-источникa> | "Y" lógico para bits variables | |

| Equipo CJNE<байт-назначения>, <байт-источник>, <смещение> | Compara y salta si no es igual | C |

| Comando CLR A | Reinicio de la batería | |

| Comando CLR | Aclarando un poco | C, poco |

| Equipo CPL A | Inversión de ak umul ora | |

| Equipo CPL | Inversión de bits | C, poco |

| Equipo DA A | Corrección decimal del acumulador para ropa de cama. | AC, C |

| Equipo DEC<байт> | Decremento | |

| Equipo DIV AB | División | C, OV |

| Equipo DJNZ<байт>, <смещение> | Decremento y transición si no es cero | |

| Equipo INC<байт> | Incremento | |

| Equipo INC DPTR | Incremento del puntero de datos | |

| Equipo JB | Saltar si el bit está configurado | |

| Equipo JBC | Salta si se establece un bit y borra ese bit | |

| Equipo JC | Salta si el acarreo está configurado | |

| Comando JMP @ A + DPTR | Transición indirecta | |

| Equipo JNB | Saltar si el bit no está configurado | |

| Equipo JNC | Saltar si el acarreo no está configurado | |

| Equipo JNZ | Saltar si el contenido de la batería no es cero | |

| Equipo JZ | Saltar si el contenido del acumulador es 0 | |

| Comando LCALL | Llamada larga | |

| Equipo LJMP | Travesía larga | |

| Comando MOV<байт-назначения>, <байт-источника> | Enviar variable de byte | |

| Comando MOV<бит-назначения>, <бит-источника> | Enviar bit de datos | C |

| Comando MOV DPTR, # data16 | Cargar puntero de datos con constante de 16 bits | |

| Comando MOVC A, @ A + ( | Enviar byte desde la memoria del programa | |

| Comando MOVX<байт приемника>, <байт источника> | Enviar datos a la memoria externa (desde la memoria externa) | |

| Equipo MUL AB | Multiplicación | C, OV |

| Comando NOP | No operacion | ordenador personal |

| Equipo ORL<байт-назначения>, <байт-источникa> | "O" lógico para bytes variables | |

| Equipo ORL C,<бит источникa> | "O" lógico para bits variables | C |

| Comando POP | Leyendo de la pila | |

| Comando PUSH | Apilado | |

| Comando RET | Regreso de subrutina | |

| Equipo RETI | Regresar de la interrupción | |

| Equipo RL A | Desplaza el contenido de la batería hacia la izquierda | |

| Equipo RLC A | Mueva el contenido de la batería hacia la izquierda a través de la bandera de transporte | |

| Equipo RR A | Desplaza el contenido de la batería hacia la derecha | |

| Equipo RRC A | Mueva el contenido de la batería hacia la derecha a través de la bandera de transporte | C |

| Comando SETB | Establecer bit | C |

| Equipo SJMP<метка> | Salto corto | |

| Equipo SUBB A,<байт источника> | Resta con préstamo | AC, C, OV |

| Intercambiar un comando | Cambio de portátiles dentro de la batería | |

| Equipo XCH A,<байт> | Intercambio del contenido del acumulador con byte variable | |

| Equipo A de XCHD, @ R1 | Cambiar un cuaderno | |

| Comando XRL<байт-назначения>, <байт-источникa> | O EXCLUSIVO lógico para bytes variables |

PLAN DE CONFERENCIAS

1. Introducción

2. Instrucciones aritméticas y lógicas

3. Comandos para la transferencia de datos

4. Operaciones booleanas

5. Instrucciones de transición

1. Introducción

Sistema de mando MCS-51 admite un solo conjunto de instrucciones, que está diseñado para ejecutar algoritmos de 8 bits para controlar dispositivos ejecutivos. Es posible utilizar métodos rápidos para direccionar la RAM interna, realizando operaciones de bits en pequeñas estructuras de datos. Existe un sistema extenso para el direccionamiento de variables de un solo bit como un tipo de datos independiente, que permite usar bits separados en comandos lógicos y de control del álgebra booleana.

Modos de direccionamiento : conjunto de comandos MCS-51 admite los siguientes modos de direccionamiento. Direccionamiento directo: el operando está definido por la dirección de 8 bits en la instrucción. El direccionamiento directo se usa solo para la mitad inferior de los datos internos y la memoria de registro SFR. Direccionamiento indirecto: la instrucción se dirige al registro que contiene la dirección del operando. Este tipo de direccionamiento se utiliza para RAM externa e interna. Los registros se pueden utilizar para indicar direcciones de 8 bits R0 y R1 banco de registro seleccionado o puntero de pila SP... Para el direccionamiento de 16 bits, solo se utiliza el registro de puntero de datos DPTR.

Instrucciones de registro : registros R0 - R7 el banco de registros actual se puede direccionar a través de instrucciones específicas que contienen un campo de 3 bits que indica el número de registro en la propia instrucción. En este caso, el campo de dirección correspondiente falta en el comando. Operaciones que utilizan registros especiales: algunas instrucciones utilizan registros individuales (por ejemplo, operaciones con batería, DPTR, etc.). En este caso, la dirección del operando no se especifica en absoluto en el comando. Está predefinido por el código de operación.

Constantes inmediatas : la constante se puede encontrar justo en el comando después del código de operación.

Direccionamiento indexado : el direccionamiento de índice solo se puede utilizar para acceder a la memoria del programa y solo en modo lectura. En este modo, las tablas se visualizan en la memoria del programa. Registro de 16 bits ( DPTR o contador de programa) indica la dirección base de la tabla deseada y el acumulador indica el punto de entrada en ella.

Conjunto de comandostiene 42 designaciones mnemotécnicas de comandos para concretar 33 funciones de este sistema. La sintaxis de la mayoría de los comandos en lenguaje ensamblador consiste en una notación de función mnemotécnica seguida de operandos que indican métodos de direccionamiento y tipos de datos. Los diferentes tipos de datos o modos de direccionamiento están determinados por los operandos establecidos, no por cambios en las designaciones mnemotécnicas.

El sistema de comando se puede dividir condicionalmente en cinco grupos: comandos aritméticos; comandos lógicos; comandos de transferencia de datos; comandos del procesador de bits; comandos de transferencia de ramificación y control. Las abreviaturas y los símbolos utilizados en el sistema de comando se muestran a continuación.

Mesa. Notación y símbolos utilizados en el sistema de comando.

|

Designación, símbolo |

Cita |

|

Batería |

|

|

Registros del banco de registro actualmente seleccionado |

|

|

El número del registro cargado especificado en el comando |

|

|

directo |

Dirección de celda de datos interna de 8 bits direccionable directamente, que puede ser una ubicación RAM de datos interna (0-127) o un registro de función especial SFR (128-255) |

|

Célula de 8 bits direccionable indirectamente de la RAM de datos interna |

|

|

8 bits directo datos incluidos en el código de operación (CPC) |

|

|

dataH |

Bits más significativos (15-8) de datos directos de 16 bits |

|

dataL |

Bits menos significativos (7-0) de datos directos de 16 bits |

|

Dirección de destino de 11 bits |

|

|

DIRECCIÓN |

Los bits menos significativos de la dirección de destino. |

|

Byte de desplazamiento con signo de 8 bits |

|

|

Bit direccionable directo, cuya dirección contiene el CPC, ubicado en la RAM de datos interna o en el registro de funciones especiales SFR |

|

|

a15, a14 ... a0 |

Bits de dirección de destino |

|

Contenido del elemento X |

|

|

Contenido en la dirección almacenada en el elemento X |

|

|

Descarga M del elemento X |

|

|

|

Operaciones: |

Los mnemónicos de función están asociados de forma única con combinaciones específicas de métodos de direccionamiento y tipos de datos. Un total de 111 combinaciones de este tipo son posibles en el sistema de comando.

2. Instrucciones aritméticas y lógicas

¿Cómo n ejemplo comando aritmético, la operación de adición se puede realizar mediante uno de los siguientes comandos.

AGREGARA,7 F 16 - agregue el número 7 al contenido del registro A F 16 y almacenar el resultado en el registro A;

AGREGARA,@ R0 - añadir al contenido del registro A el número cuya dirección (@ – comercial a ) se almacena en el registro R 0 (direccionamiento indirecto) y almacena el resultado en el registro A;

AÑADIR A, R7- agregar el contenido del registro al contenido del registro A R 7 y guarde el resultado en el registro A;

AÑADIR A, # 127- agregue al contenido del registro A el número, cuya dirección de almacenamiento es 127 ( # - símbolo de número), y guarde el resultado en el registro T- re A.

Todas las instrucciones aritméticas se ejecutan en un ciclo de máquina con la excepción de la instrucción INC DPTR(desplazamiento del puntero de datos DPTR al byte siguiente), que requiere dos ciclos de máquina, así como operaciones de multiplicación y división realizadas en 4 ciclos de máquina. Cualquier byte en la memoria de datos interna se puede incrementar y disminuir sin usar la batería.

Instrucciones MUL AB realiza la multiplicación de los datos en el acumulador por los datos en el registro B, colocando el producto en los registros A (mitad baja) y B (mitad alta).

Instrucciones DIV AB divide el contenido del acumulador por el valor del registro B, dejando el resto en B y el cociente en el acumulador.

Instrucciones DA A está diseñado para operaciones aritméticas binario-decimal (operaciones aritméticas sobre números representados en código binario-decimal). No convierte binario a decimal binario, pero solo proporciona el resultado correcto al sumar dos números BCD.

Ejemplo comando lógico: La operación lógica AND se puede realizar mediante uno de los siguientes comandos:

ANLA,7 F 16 - multiplicación lógica del contenido del registro A por el número 7 F 16 y el resultado se almacena en el registro A;

ANLA,@ R1 - multiplicación lógica del contenido del registro A por el número cuya dirección está almacenada en el registro R 1 (direccionamiento indirecto) y almacenar el resultado en el registro A;

ANL A, R6- multiplicación lógica del contenido del registro A por el contenido del registro R 6 y almacene el resultado en el registro A;

ANL A, # 53 - multiplicación lógica del contenido del registro A por un número, cuya dirección de ubicación de almacenamiento es 53 16, y el resultado se almacena en el registro A.

Todas las operaciones lógicas sobre el contenido del acumulador se realizan en un ciclo de máquina, el resto, en dos. Las operaciones lógicas se pueden realizar en cualquiera de los 128 bytes inferiores de la memoria interna de datos o en cualquier registro SFR (registros de funciones especiales) en modo de direccionamiento directo sin usar batería.

Las operaciones de desplazamiento cíclico RL A, RLC A, etc. mueven el contenido del acumulador un bit hacia la derecha o hacia la izquierda. En el caso de un desplazamiento cíclico a la izquierda, el bit menos significativo se mueve a la posición más significativa. En el caso de un desplazamiento cíclico a la derecha, ocurre lo contrario.

Operación INTERCAMBIAR A intercambia los cuadernos junior y senior en el acumulador.

3. Comandos de transferencia de datos

Mando MOV dest, src le permite transferir datos entre las celdas de la RAM interna o el área de registro de funciones especiales SFR sin usar batería. En este caso, el trabajo con la mitad superior de la RAM interna se puede realizar solo en el modo de direccionamiento indirecto y el acceso a los registros. SFR- solo en modo direccionamiento directo.

En todos los microcircuitos MCS-51 la pila se asigna directamente a la memoria residente de datos y crece hacia arriba. Instrucciones EMPUJAR primero incrementa el valor en el registro de puntero de pila SP y luego inserta un byte de datos en la pila. Comandos EMPUJAR y MÚSICA POP se utiliza solo en el modo de direccionamiento directo (escribiendo o restaurando un byte), pero la pila siempre es accesible cuando se direcciona indirectamente a través de un registro SP... Por tanto, la pila puede utilizar los 128 bytes superiores de la memoria de datos. Las mismas consideraciones excluyen la posibilidad de utilizar instrucciones de pila para direccionar registros. SFR.

Las instrucciones de transferencia de datos incluyen una operación de transferencia de 16 bits MOV DPTR, # data16 que se utiliza para inicializar el registro de puntero de datos DPTR al visualizar tablas en la memoria del programa o al acceder a la memoria de datos externa.

Operación XCH A, byte utilizado para intercambiar datos entre el acumulador y el byte direccionado. Mando XCHD A, @ Ri es similar al anterior, pero se realiza solo para tétradas inferiores que participan en el intercambio de operandos.

Solo se utiliza el direccionamiento indirecto para acceder a la memoria de datos externa. En el caso de direcciones de un solo byte, se utilizan registros R0 o R1 el banco de registros actual, y para 16 bits - el registro de puntero de datos DPTR... Con cualquier método de acceso a la memoria de datos externa, el acumulador desempeña el papel de fuente o receptor de información.

Para acceder a las tablas ubicadas en la memoria del programa, use los comandos:

MOVC A, @ A + DPTR ;

MOVC A, @ A + ordenador personal .

El contenido del registro de puntero de datos se utiliza como dirección base de la tabla. DPTR o ordenador personal(contador de programa), y el desplazamiento se toma de A... Estos comandos se utilizan exclusivamente para leer datos de la memoria del programa, pero no para escribir en ellos.

4. Operaciones booleanas

Microcircuitos MCS-51 contienen un procesador "booleano". La RAM interna tiene 128 bits directamente direccionables. Espacio de registro de funciones especiales SFR también puede admitir campos de hasta 128 bits. Las instrucciones de bit realizan saltos condicionales, transferencias, volcados, inversiones y operaciones Y y O. Todos los bits especificados están disponibles en modo de direccionamiento directo.

Llevar poco CF en el registro de funciones especiales "palabra de estado del programa PSW»Se utiliza como un acumulador de un bit de un procesador booleano.

5. Instrucciones de transición

Las direcciones de las operaciones de transición se indican en lenguaje ensamblador mediante una etiqueta o mediante un valor real en el espacio de memoria del programa. Las direcciones de rama condicional se ensamblan en un desplazamiento relativo: un byte de signo agregado al contador del programa ordenador personal si se cumple la condición de transición. Los límites de tales transiciones se encuentran entre menos 128 y 127 con respecto al primer byte que sigue a la instrucción. En el registro de funciones especiales "palabra de estado del programa PSW"Falta la bandera cero, por lo que las instrucciones JZ y JNZ verifique la condición "igual a cero" mientras prueba los datos en el acumulador.

Hay tres tipos de comando de rama incondicional: SJMP, LJMP y AJMP- diferente en el formato de la dirección de destino. Instrucciones SJMP codifica la dirección como un desplazamiento relativo y ocupa dos bytes. La distancia de salto está limitada a un rango de menos 128 a 127 bytes en relación con la instrucción siguiente SJMP.

En las instrucciones LJMP la dirección de destino se utiliza como una constante de 16 bits. La longitud del comando es de tres bytes. La dirección de destino se puede ubicar en cualquier lugar de la memoria del programa.

Mando AJMP utiliza una constante de dirección de 11 bits. El comando consta de dos bytes. Cuando se ejecuta esta instrucción, los 11 bits inferiores del contador de direcciones se reemplazan con la dirección de 11 bits de la instrucción. Los cinco bits más significativos del contador de software ordenador personal permanece inalterable. Por lo tanto, la transición se puede realizar dentro de un bloque de 2K bytes, en el que se ubica la instrucción que sigue a la instrucción AJMP.

Hay dos tipos de llamadas a subrutinas de comando: LCALL y UNA LLAMADA... Instrucciones LCALL utiliza la dirección de 16 bits de la subrutina llamada. En este caso, la subrutina se puede ubicar en cualquier lugar de la memoria del programa. Instrucciones UNA LLAMADA utiliza una dirección de subrutina de 11 bits. En este caso, la subrutina llamada debe estar ubicada en un bloque de 2K bytes con la siguiente instrucción UNA LLAMADA... Ambas versiones del comando colocan la dirección del siguiente comando en la pila y la cargan en el contador del programa. ordenador personal el nuevo valor correspondiente.

La subrutina termina con una instrucción RETIRADO para volver a la instrucción que sigue al comando LLAMA... Esta instrucción extrae la dirección de retorno de la pila y la carga en el contador del programa. ordenador personal ... Instrucciones RETI utilizado para volver de las rutinas del servicio de interrupción. La unica diferencia RETI de RETIRADO es eso RETI informa al sistema que el manejo de interrupciones ha finalizado. Si en el momento de la ejecución RETI no hay otras interrupciones, entonces es idéntico RETIRADO.

Instrucciones DJNZ diseñado para controlar ciclos. Para ejecutar el ciclo norte una vez es necesario cargar bytes con el valor norte y cierra el cuerpo del bucle con el comando DJNZ indicando el inicio del ciclo.

Mando CJNE compara sus dos operandos como enteros sin signo y salta a la dirección especificada en él si los operandos comparados no son iguales. Si el primer operando es menor que el segundo, entonces el bit de acarreo CF está configurado en "1".

Todos los comandos en forma ensamblada ocupan 1, 2 o 3 bytes.

Arquitectura de microcontrolador

Comprender la arquitectura de los microcontroladores es clave a la hora de aprender lenguajes de programación como el ensamblaje. La estructura del ensamblador, el formato de sus instrucciones, el direccionamiento de los operandos, etc., están completamente determinados por la arquitectura. El propósito de estudiar arquitectura es:

· Identificación de un conjunto de registros disponibles para programación, su finalidad funcional y estructura;

· Comprender la organización de la memoria de acceso aleatorio y el orden de su uso;

· Familiaridad con los tipos de datos;

· Estudio del formato de las instrucciones de la máquina;

· Aclaración de la organización del manejo de interrupciones.

La arquitectura de la familia MCS-51 está predeterminada en gran medida por su propósito: la construcción de dispositivos digitales compactos y baratos. Todas las funciones de MK se implementan utilizando un solo microcircuito. La familia MCS-51 incluye varios microcircuitos, desde los microcontroladores más simples hasta los más complejos. Los microcontroladores de la familia MCS-51 le permiten realizar tanto tareas de control para varios dispositivos como implementar nodos de circuitos analógicos individuales. Todos los microcircuitos de esta familia funcionan con el mismo sistema de comando, la mayoría de ellos se ejecutan en los mismos paquetes con el mismo pinout (numeración de pines del paquete). Esto permite el uso de microcircuitos de diferentes fabricantes (como Intel, Dallas, Atmel, Philips, etc.) para el dispositivo desarrollado sin alterar el diagrama de circuito del dispositivo y el programa.

El MCS-51 se fabrica de acuerdo con la arquitectura de Harvard, donde la memoria del programa y los espacios de direcciones de datos están separados.

El diagrama de bloques del controlador se muestra en la Figura 2.3 y consta de las siguientes unidades funcionales principales: unidad de control, dispositivo aritmético lógico, unidad de temporizador / contador, interfaz serial e interrupciones, contador de programa (contador de comando), memoria de datos y memoria de programa.

El intercambio bidireccional se realiza mediante una autopista de datos interna de 8 bits. Echemos un vistazo más de cerca al propósito de cada bloque. Casi todos los representantes de la familia MCS-51 se construyen de acuerdo con este esquema. Varios microcircuitos de esta familia difieren solo en registros de propósito especial (incluido el número de puertos). El sistema de comando de todos los controladores de la familia MCS-51 contiene 111 comandos básicos con un formato de 1, 2 o 3 bytes y no cambia al pasar de un microcircuito a otro. Esto proporciona una excelente portabilidad de programas de un microcircuito a otro.

Unidad de control y sincronización(Timing and Control) está diseñado para generar señales de sincronización y control que aseguren la coordinación de la operación conjunta de las unidades OEVM en todos los modos permisibles de su operación. La unidad de control incluye:

- dispositivo de formación de franjas horarias,

- circuito combinado de entrada-salida,

- registro de comando,

- decodificador de comandos.

Entrada y fin de semana señales de la unidad de control y sincronización:

1 PSEN- resolución de la memoria del programa;

2 Cerveza inglesa- señal de salida de permiso de retención de dirección;

3 PROG- señal de programación;

4 EA- bloqueo del trabajo con memoria interna;

5 VPP- voltaje de programación;

6 RST- señal de reinicio general.

Se necesita un dispositivo de temporización para sincronizar la secuencia de estados de la CPU que forman un ciclo de máquina, así como para el correcto funcionamiento de todos los pestillos internos y búferes de salida de los puertos. El ciclo de la máquina consta de seis estados consecutivos (estados) de S1 a S6, cada uno de los cuales, a su vez, se subdivide en dos fases:

fase 1 (Fase 1 - P1) y fase 2 (Fase 2 - P2). Por tanto, un ciclo de máquina se puede definir como una secuencia de intervalos de tiempo S1P1, S1P2, S2P1, ...., S6P2. La duración de la fase es igual al período de repetición del pulso de reloj, por lo que el ciclo de la máquina toma 12 períodos de reloj.

El número de ciclos de la máquina determina la duración de la ejecución de la instrucción. Casi todas las instrucciones se ejecutan en uno o dos ciclos de máquina, excepto las instrucciones de multiplicación y división, cuyo tiempo de ejecución es de cuatro ciclos de máquina. La lógica de entrada y salida está diseñada para recibir y emitir señales que proporcionan intercambio de información con dispositivos externos a través de los puertos de entrada / salida P0-P3.

Registro de comando está diseñado para grabar y almacenar el código de operación de 8 bits del comando que se está ejecutando. El código de operación, con la ayuda del decodificador de comandos y la lógica de control de la computadora, se convierte en el microprograma de ejecución de comandos.

Figura 2.3. Diagrama de bloques de un microcontrolador de un solo chip Intel 8051

(Familia MCS-51)

Unidad aritmética lógica(ALU) es un dispositivo paralelo de ocho bits que realiza operaciones aritméticas y lógicas. ALU consta de:

- tenencia de registros -TMP1 y TMP2,

- Constantes de ROM,

- sumador,

- registro adicional - registro B,

- batería - ACC,

- registro de palabra de estado del programa (registro de banderas) - PSW.

Holding registros TMP1, TMP2- registros de ocho bits destinados a recibir y almacenar operandos mientras duren las operaciones en ellos. Estos registros no son accesibles mediante programación.

Constantes ROM proporciona la generación de un código de corrección para la representación de datos binario-decimal, un código de máscara para operaciones de bits y un código constante.

Sumador paralelo de ocho bits es un circuito de tipo combinación con acarreo secuencial, diseñado para realizar operaciones aritméticas de suma, resta y operaciones lógicas de suma, multiplicación, desigual e idéntica.

Registro B- un registro de ocho bits utilizado durante las operaciones de multiplicación y división. Para otras instrucciones, puede verse como un registro superoperativo adicional.

Batería- un registro de ocho bits destinado a recibir y almacenar el resultado obtenido al realizar operaciones aritmético-lógicas u operaciones de desplazamiento.

Registro de estado del programa PSW (Programm Status Word) está destinado a almacenar la palabra de estado de los comandos que se están ejecutando. Al ejecutar muchos comandos en la ALU, se generan varios signos de operación (banderas), que se fijan en el registro de la palabra de estado del programa (PSW). Mesa 1 enumera las banderas de PSW, da sus nombres simbólicos y describe las condiciones para su formación.

Interrupción y bloqueo en serie - UART (receptor / transmisor asíncrono universal) está destinado a la organización de entrada - salida de flujos secuenciales de información y la organización de un sistema para interrumpir programas.Por definición, una interrupción significa una interrupción temporal del proceso de cálculo principal para realizar algunas acciones planificadas o no planificadas causadas por el funcionamiento del hardware o programa.

Estas acciones pueden ser de naturaleza de servicio, ser una solicitud del programa de usuario para realizar mantenimiento o ser una reacción a situaciones anormales.

Cómo ganar dinero en Minecraft: crear mapas, alojar un servidor y vender recursos Crear un servidor de Minecraft

Cómo ganar dinero en Minecraft: crear mapas, alojar un servidor y vender recursos Crear un servidor de Minecraft Cómo configurar Skype en Android Cómo usar la versión móvil de Skype

Cómo configurar Skype en Android Cómo usar la versión móvil de Skype Los conceptos básicos de la programación para principiantes: dónde comenzar a aprender, los mejores cursos y lecciones Lo que necesita para estudiar como programador

Los conceptos básicos de la programación para principiantes: dónde comenzar a aprender, los mejores cursos y lecciones Lo que necesita para estudiar como programador Marinero experto Marinero experto ¿Cuánto es 1 punto en grados?

Marinero experto Marinero experto ¿Cuánto es 1 punto en grados? Cómo cambiar un cartucho en una impresora: instrucciones paso a paso

Cómo cambiar un cartucho en una impresora: instrucciones paso a paso Acerca de los microcontroladores para principiantes: la historia de la creación, los principales tipos y diferencias ¿Cuál es la diferencia entre un microprocesador y un microcontrolador?

Acerca de los microcontroladores para principiantes: la historia de la creación, los principales tipos y diferencias ¿Cuál es la diferencia entre un microprocesador y un microcontrolador? Espacio de información personal del docente (a partir de la experiencia laboral) IV

Espacio de información personal del docente (a partir de la experiencia laboral) IV